Курсовая работа: Вычислительная система обработки данных в реальном времени

1. Максимальная разрядность интерфейса системной шины равна 16. Данное обстоятельство обуславливает выбрать разрядность входного и выходного слова 16 бит;

2. Так как задан комплект К1810 в минимальном режиме, то потребуется использовать следующие микросхемы: генератор тактовых импульсов К1810ГФ84, два буферных регистра К1810ИР82, два двунаправленных шинных формирователя К1810ВА86;

3. Цифровой сигнал 16-ти битовый, поэтому необходимо использовать два буферных регистра, каждый разрядностью 8 бит, необходимые для разделения входного сигнала на 16 разрядные слова. Если регистры не использовать, то большая часть данных будет потеряна;

4. Проанализировав функцию, ясно что в при ее выполнении можно обойтись внутренними регистрами микропроцессора, поэтому нет необходимости использовать ОЗУ. Вся программа хранится в ПЗУ;

5. В качестве параллельного порта будет использовать микросхему К580ВВ55, у которой 3 8-разрядных порта, для вывода данных будем использовать 2 из них, то есть обеспечим передачу слова;

6. В параллельном порте будет использовать бит 0 в порте С в качестве бита готовности данных, по которым ПЭВМ определит, что выходные данные поступили в порты А и В.

Анализ исходных данных позволяет выбрать элементы, назначение и описание выводов которых приведено в следующем пункте курсовой работы.

Выбор элементной базы

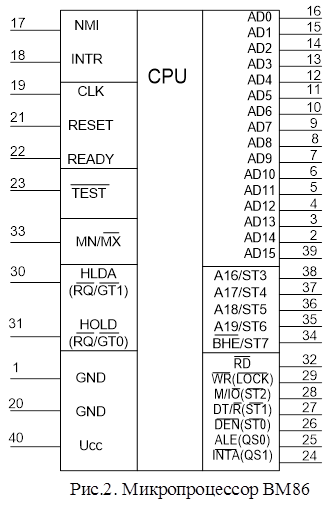

Микросхема К1810ВМ86

Микропроцессор К1810ВМ86 представляет собой однокристальный 16-битовый МП работающий в данной вычислительной системе в минимальном режиме. Этот модуль производит чтение ПЗУ, а также чтение и запись в порты ввода-вывода. Условное графическое обозначение МП К1810ВМ86 приведено на рис.2. Опишем его выводы, используемые при проектировании системы.

AD15- AD0 - мультиплексная двунаправленная шина адреса/данных, по которой с разделением во времени передаются адресная информация и данные;

![]() - разрешение старшего байта, активный сигнал означает, что по старшей половине AD15-AD8 передаются 8 - битовые данные. Он защелкивается во внешнем регистре адреса и используется как дополнительный адресный выход, определяющий доступ к старшему банку памяти. Совместное использование

- разрешение старшего байта, активный сигнал означает, что по старшей половине AD15-AD8 передаются 8 - битовые данные. Он защелкивается во внешнем регистре адреса и используется как дополнительный адресный выход, определяющий доступ к старшему банку памяти. Совместное использование ![]() и младшей линии адреса А0 для дешифрации адресов позволяет осуществлять передачу слов или отдельных байтов по шине АD;

и младшей линии адреса А0 для дешифрации адресов позволяет осуществлять передачу слов или отдельных байтов по шине АD;

ALE - строб адреса (разрешение защелкивания адреса), выдается в начале каждого цикла шины и используется для записи адреса в регистр - защелку, т.е. для демультиплексирования шины AD;

![]() - строб данных (разрешение передачи данных). Выдается в циклах чтения, записи и разрешения входа шинных формирователей;

- строб данных (разрешение передачи данных). Выдается в циклах чтения, записи и разрешения входа шинных формирователей;

![]() - чтение, идентифицирует выполнения цикла чтения из ЗУ или внешнего устройства (в зависимости от значения сигнала

- чтение, идентифицирует выполнения цикла чтения из ЗУ или внешнего устройства (в зависимости от значения сигнала ![]() ). Указывает этим устройствам на необходимость выдачи данных на шину;

). Указывает этим устройствам на необходимость выдачи данных на шину;

![]() - запись, указывает на выполнение цикла записи ЗУ или ВУ и сопровождает данные, выдаваемые микропроцессором на шину;

- запись, указывает на выполнение цикла записи ЗУ или ВУ и сопровождает данные, выдаваемые микропроцессором на шину;

![]() - является признаком обращения к ЗУ (

- является признаком обращения к ЗУ (![]() =1) или ВУ и используется для разделения адресного пространства памяти и ввода/вывода.

=1) или ВУ и используется для разделения адресного пространства памяти и ввода/вывода. ![]() =0 появляется только при выполнении команд ввода (IN) и вывода (OUT);

=0 появляется только при выполнении команд ввода (IN) и вывода (OUT);

![]() - передача/прием данных, определяет направление передачи по шине AD:

- передача/прием данных, определяет направление передачи по шине AD: ![]() =1 - запись данных из ЗУ или ВУ в МП. Предназначен для управления шинными формирователями и действует на протяжении всего цикла шины, как и сигнал

=1 - запись данных из ЗУ или ВУ в МП. Предназначен для управления шинными формирователями и действует на протяжении всего цикла шины, как и сигнал ![]() ;

;

READY - готовность, указывает на то, что адресуемое в данном цикле устройство готово к обмену данными. Если устройство не готово к взаимодействию с МП, оно выдает сигнал READY=0, и МП переходит в состояние ожидания. В этом случае между тактами Т3 и Т4 цикла шины появляется необходимое число тактов ожидания TW. После установки сигнала READY=1 МП выходит из состояния ожидания и возобновляет работу;

CLK - тактовая синхронизация (тактирование). Сигнал синхронизации от внешнего генератора тактовых импульсов, предназначен для синхронизации МП. Используется серия тактовых импульсов CLK с периодом повторения T, равным 200 - 500 нс.;

RESET - сброс, переводит МП в определенное начальное состояние, в котором сброшены сегментные регистры (кроме CS, все разряды которого устанавливаются в единичное состояние), указатель команд IP, все флаги, регистры очереди команд и все внутренние триггеры в устройстве управления. Сигнал RESET не влияет на состояние общих регистров, которые устанавливаются в начальное состояние программным путем. На время действия сигнала RESET все выходы, имеющие три состояния, становятся пассивными. Минимальная продолжительность сигнала RESET при первом включении МП составляет 50 мкс., а при повторном запуске - четыре такта синхронизации. После снятия сигнала RESET работа МП возобновляется из начального состояния;

![]() - минимальный/максимальный режим. Сигнал на этот входе определяет режимы работы МП: 1 - минимальный, 0 - максимальный. Используемый режим в работе минимальный, поэтому на него нужно подавать напряжение.

- минимальный/максимальный режим. Сигнал на этот входе определяет режимы работы МП: 1 - минимальный, 0 - максимальный. Используемый режим в работе минимальный, поэтому на него нужно подавать напряжение.

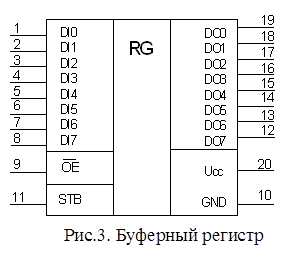

Микросхема К1810ИР82.

Буферный регистр представляет собой 8 - разрядный параллельный регистр с тристабильными выходами и используется для организации адресных защелок и портов ввода - ввода. Графическое обозначение приведено на рис.3. Опишем назначение выводов этой микросхемы.

DI7- DI0 - линии входных данных;

DO7- DO0 - линии выходных данных;

STB - вход стробирующего сигнала, при сигнале высокого уровня на нем состояние входных линий DI7-DI0 передается на выходные линии DO7-DO0. Защелкивание в информационных триггерах осуществляется при переходе сигнала STB от высокого уровня к низкому;

![]() - разрешение выдачи данных. При

- разрешение выдачи данных. При ![]() = 0 буфер отпирается, при

= 0 буфер отпирается, при ![]() = 1 он устанавливается в Z- состояние.

= 1 он устанавливается в Z- состояние.