Курсовая работа: Вычислительная система обработки данных в реальном времени

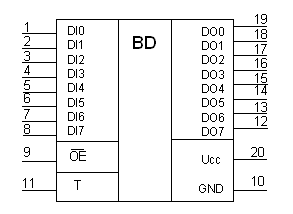

Шинный формирователь представляет 8 - разрядный параллельный приемопередатчик с тристабильными выходами и используется как буферное устройство шины данных в микропроцессорных системах. Графическое изображение приведено на рис.4. Опишем выводы микросхемы.

DI7- DI0 - вход/выход линий данных. В зависимости от состояния входа Т они могут быть входными, если на Т сигнал высокого уровня, и выходными, если на Т сигнал низкого уровня;

DО7- DО0 - вход/выход линий данных. Они являются входными, если на Т сигнал низкого уровня, и выходными, если на Т сигнал высокого уровня;

Т - вход управления направлением передачи. При Т=0 осуществляется передача от DO к DI, при Т=1 - от DI к DO;

![]() - вход разрешения передачи. При

- вход разрешения передачи. При ![]() =0 снимается Z- состояние с выхода формирователя, выбранного по входу Т.

=0 снимается Z- состояние с выхода формирователя, выбранного по входу Т.

Микросхема К1810ГФ84.

Рис.4. Шинный формирователь

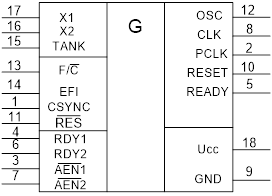

Генератор тактовых импульсов предназначен для управления ЦП К1810ВМ86 и периферийными устройствами. Графическое изображение микросхемы приведено на рис.5. Опишем используемые ее выводы.

Х1 и Х2 - выводы для подключения кварцевого резонатора;

![]() - вход для подключение RC- цепи, обеспечивающий автоматическое формирование сигнала сброса при включении источника питания;

- вход для подключение RC- цепи, обеспечивающий автоматическое формирование сигнала сброса при включении источника питания;

![]() - вход используется для выбора задающего генератора. При

- вход используется для выбора задающего генератора. При ![]() =0 соответствует внутреннему генератору (кварцевый резонатор), а при

=0 соответствует внутреннему генератору (кварцевый резонатор), а при ![]() =1 - внешнему генератору импульсов, подключаемый на вход ЕFI;

=1 - внешнему генератору импульсов, подключаемый на вход ЕFI;

RDY1 - вход сигнала готовности от устройств, подключаемых к каналу системы;

![]() - вход разрешения адресации для сигнала готовности RDY1;

- вход разрешения адресации для сигнала готовности RDY1;

С LK - выход тактовых импульсов, их частота равна 5Мгц и образуется делением частоты задающего генератора на 3 (его частота 15Мгц);

READY - выход сигнала готовности, синхронизированный с задним фронтом сигнала CLK. Он позволяет обеспечить сопряжение во времени работы МП с работой внешних устройств, имеющих меньшее быстродействие;

RESET - выход сигнала сброса, синхронизированного с задним фронтом сигнала СLK. После поступления сигнала RESET МП прекращает работу и остается в режиме ожидания до окончания этого импульса. Затем начинается процесс инициализации МП, который длится 10 тактов.

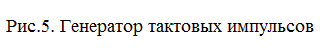

Микросхема К580ВВ55.

БИС параллельного интерфейса предназначена для организации ввода/вывода параллельной информации различного формата. Структурная схема микросхемы приведена на Рис.6. Опишем используемые ее выводы.

D7- D0 - вход/выход данных;

![]() - чтение. Низкий уровень сигнала разрешает считывание информации из регистра, адресуемого по входам А0, А1 на шину D7. D0;

- чтение. Низкий уровень сигнала разрешает считывание информации из регистра, адресуемого по входам А0, А1 на шину D7. D0;

![]() - запись. Низкий уровень сигнала разрешает запись информации с шины D7. D0 в порт микросхемы, адресуемый по входам А0 и А1;

- запись. Низкий уровень сигнала разрешает запись информации с шины D7. D0 в порт микросхемы, адресуемый по входам А0 и А1;

A0 и A1 - входы для адресации внутренних регистров.00 - порт А, 01 - порт В, 10 - порт С, 11 - порт управляющего слова, которое устанавливает работу микросхемы в один из трех режимов;

![]() - выбор микросхемы, низкий уровень подаваемого сигнала подключает ее к системной шине;

- выбор микросхемы, низкий уровень подаваемого сигнала подключает ее к системной шине;

RS - сброс, высокий уровень сигнала обнуляет регистр управляющего слова и устанавливает все порты в режим ввода;

РА7-РА0 - вход/выход канала А;

РВ7-РВ0 - вход/выход канала В;