Реферат: Физические основы действия современных компьютеров

Схем включения блоков памяти

Схем включения блоков памяти

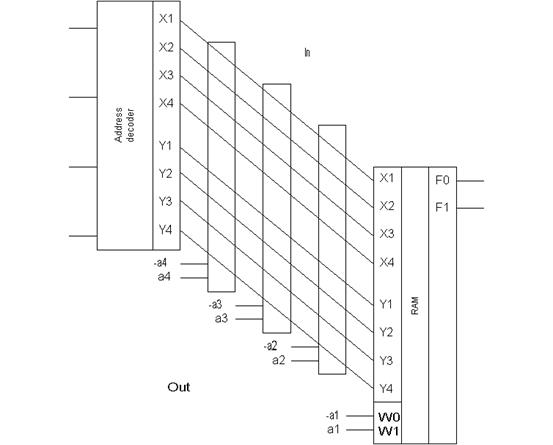

Так как матрица-накопитель одной рассматриваемой микросхемы содержит 16 элементов памяти, то при параллельном включении четырех таких микросхем получается запоминающее устройство, которое может одновременно хранить 16 четырехразрядных чисел (заметим в скобках, что современные устройства памяти оперируют 64-разрядными числами). Для адресации этих чисел необходимо иметь 16 различных адресных сигналов, что можно получить при четырехэлементном коде адреса. Например, при коде адреса 0000 сигналы единичного уровня появятся на шинах с номерами 1, которые на всех схемах выбирают элемента памяти с адресом 1.1. Таким образом, в первой схеме запишется 1й разряд числа, во второй – второй и т.д. Часть запоминающего устройства, предназначенная для хранения многоразрядного числа, называется ячейкой памяти.

Статическое ЗУ

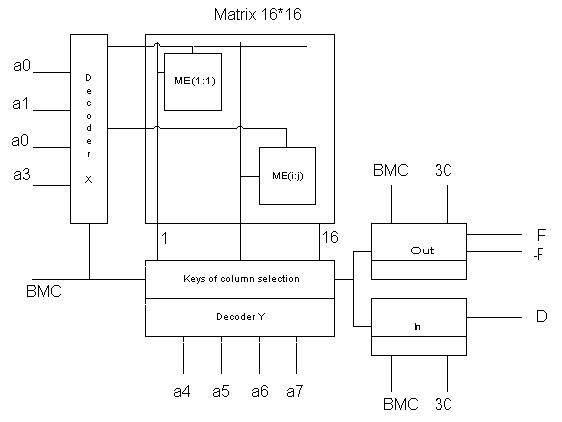

Как уже отмечалось, в статическом ЗУ роль элемента памяти выполняет триггер. Возьмем матрицу из 16*16=256 элементов, т.е. организация накопителя будет 256*1 бит. Для обращения к такому ОЗУ необходимо подвести к нему сигнал,. разрешающий работу (ВМС – выборка микросхемы), к информационным входу и выходу, и восьмиразрядный код адреса к адресным входа дешифраторов.

Дешифратор управляет ключами выборки строк и столбцов, которые, в свою очередь вырабатывают сигналы, соединяющий выбранный элемент памяти и шину ввода-вывода. Сигналом запись-считывание (ЗС) устанавливается режим работы микросхемы.

При поступлении единичного уровня сигналов ЗС и ВМС открывается схема ввода информации. Через шину ввода-вывода и открытый ключ выборки столбца информация через вход поступает на выбранный элемент памяти.

При нулевом сигнале ЗС и сигнале ВМС открывается схема вывода информации на выход. При отсутствии сигналов ЗС и ВМС выход микросхемы отключается от внешней шины.

Схема работы статической памяти.

Схема работы статической памяти.

Динамическое ОЗУ

Динамическому ОЗУ нужна периодическая перезапись (регенерация) информации для ее хранения. Возьмем, например схему с емкостью 4096*1 бит с матрицей 64*64=4096 элементов памяти. В ней необходимо иметь 64 усилителя считывания, и два шестиразрядных регистра для хранения кода адреса, дешифраторы строк столбцов с 64 выходами каждый, устройство ввода-вывода и устройство управления и синхронизации, которое будет формировать управляющие сигналы. Элементом память в данном случае будет конденсатор, который с помощью ключевой схемы на транзисторе будет подключаться к разрядной шине. При совпадении выходного сигнала дешифратора столбца и управляющего сигнала F3 открываются ключи выборки столбцов, шины ввода-вывода соединяются с выбранной разрядной шиной – производится считывание или запись информации.

Микросхема управляется четырьмя сигналами: кодом адреса, тактовым сигналом, выборки микросхемы и записи-считывания.

Сигналы адреса (выборка элементов памяти_ поступают на регистры строк и столбцов для выбора элемента памяти. Обращение к матрице по адресным входам разрешается тактовым сигналом. Код адреса после записи в регистрах дешифруется. Одновременно запускаются формирователи F1 и через него - F2, управляющие выбором строки. Также от F1 селектором строк разрядные шины подключается к конденсаторам опорных элементов. Из-за того, что собственная емкость шин больше, чем емкость запоминающего конденсатора, разность потенциалов между ними при их подключении друг к другу будет незначительна. Поэтому необходим весьма чувствительный усилитель считывания.

Сигнал F2 включает усилитель считывания и происходит регенерация информации во всех элементах памяти выбранной строки.

По сигналу ВМС запускается формирователь F3 и через него F4, которые коммутируют цеп вывода информации и шины ввода-вывода с разрядной шиной через транзисторные ключи. Информация считывается. С окончанием тактового сигнала все узлы микросхемы возвращаются в исходное состояние.

Поскольку динамической памяти необходима регенерация, число циклов которой будет равно число строк в матрице. Этот цикл идет когда нет разрешающего сигнала ВМС. Для этого цикла необходимы счетчик, коммутатор, триггер и генератор регенерации, синхронизированный тактовым сигналом.

Системная память: взгляд в будущее

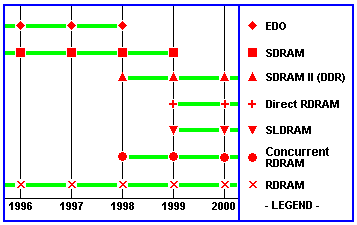

До 2000 года в мир персональных компьютеров войдет несколько новых архитектур высокоскоростной памяти. В настоящее время, с конца 1997 года по начало 1998 основная память PC осуществляет эволюцию от EDO RAM к SDRAM - синхронную память, которая, как ожидается будет доминировать на рынке с конца 1997 года. Графические и мультимедийные системы в которых сегодня применяется RDRAM перейдет к концу года на Concurent (конкурентную) RDRAM. Итак, в период между 1997 и 2000 годом будут развиваться пять основных технологий:

SDRAM II (DDR);

SLDRAM (SyncLink);

RAMBus (RDRAM);

Concurent RAMBus;

Direct RAMBus.

График, приведенный ниже, приближенно демонстрирует время появления и

применения будущих технологий памяти.

Крайне сложно предсказать, на чем остановится прогресс. Все десять крупнейших производителей памяти, такие как Samsung, Toshiba и Hitachi, разрабатывающие Direct RDRAM, также продолжают развивать агрессивную политику, направленную на развитие альтернативных технологий памяти следующих поколений, таких как DDR и SLDRAM. В связи с этим образовалось любопытное объединение конкурентов. Тем не менее, несмотря на некоторую неизвестность, попытаемся дать общий обзор и объяснение того, что и где будет применяться в ближайшее время.

В первой части материала описываются причины, которые заставляют переходить к новым технологиям памяти. Во второй части статьи приводится описание шести основных технологий, их сходства и различия. Необходимость увеличения производительности системы памяти.

Быстрое развитие аппаратных средств и программного обеспечения привело к тому, что вопрос эффективности встает на первое место. Фактически, несколько лет назад, Гордон Мур, президент корпорации Intel, предсказал, что мощность центрального процессора в персональном компьютере будет удваиваться каждые 18 месяцев (Закон Мура). Мур оказался прав. С 1980 года до настоящего момента тактовая частота процессора Intel, установленного в персональном компьютере возрасла в 60 раз (с 5 до 300MHz). Однако, за то же время, частота, на которой работает системная память со страничной организацией (FPM), возрасла всего в пять раз. Даже применение EDO RAM и SDRAM увеличило производительность системы памяти всего в десять раз. Таким образом, между производительностью памяти и процессора образовался разрыв. В то время как процессоры совершенствовались в архитектуре, производство памяти претерпевало лишь технологические изменения. Емкость одной микросхемы DRAM увеличилась с 1Мбит до 64Мбит. Это позволило наращивать объем применяемой в компьютерах памяти, но изменения технологии в плане увеличения производительности DRAM не произошло. Короче говоря, скорость передачи не увеличилась вслед за объемом.

Что касается потребностей, то в следствии применения нового программного обеспечения и средств мультимедиа, потребность в быстродействующей памяти нарастала. С увеличением частоты процессора, и дополнительным использованием средств мультимедиа новым программным обеспечением, не далек тот день, когда для нормальной работы PC будут необходимы гигабайты памяти. На этот процесс также должно повлиять внедрение и развитие современных операционных систем, например Windows NT.