Реферат: Логические элементы и их электронные аналоги

Рис. 8. Логический элемент НЕ, выполненный на МОП-транзисторах с n-каналом (а), комплиментарной паре МОП-транзисторов с n- и р-каналами (б).

Логический элемент И – НЕ.

![]()

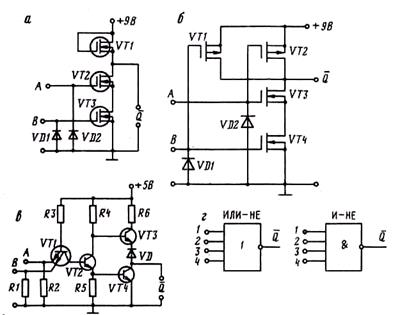

![]() Более универсален элемент И-НЕ, позволяющий одновременно с операцией логического умножения выполнить и отрицание, тем более что в большинстве случаев это не усложняет схемы. Например, на рис. 9, а приведен МОП-вариант схемы логического элемента И-НЕ. Транзистор VT1 используется вместо сопротивления нагрузки и постоянно открыт, ибо на его затвор подается напряжение в отпирающей полярности. Если на затворы транзисторов VT2 и VT3 поданы напряжения логического 0, то они заперты, тока не проводят и на выходе Q действует почти полное напряжение питания, т. е. напряжение логической 1. Если подается напряжение логической 1 только на один из входов А или В, то состояние схемы не изменяется и напряжение на выходе остается неизменным. Однако, если на оба входа действуют напряжения логических 1, то оба транзистора VT2 и VT3 отпираются, их внутреннее сопротивление уменьшается (до 500 - 1000 Ом) и напряжение на выходе Q также становится весьма малым, т. е. на выходе действует логический 0 - в полном соответствии с таблицей истинности И-НЕ (табл. 4.).

Более универсален элемент И-НЕ, позволяющий одновременно с операцией логического умножения выполнить и отрицание, тем более что в большинстве случаев это не усложняет схемы. Например, на рис. 9, а приведен МОП-вариант схемы логического элемента И-НЕ. Транзистор VT1 используется вместо сопротивления нагрузки и постоянно открыт, ибо на его затвор подается напряжение в отпирающей полярности. Если на затворы транзисторов VT2 и VT3 поданы напряжения логического 0, то они заперты, тока не проводят и на выходе Q действует почти полное напряжение питания, т. е. напряжение логической 1. Если подается напряжение логической 1 только на один из входов А или В, то состояние схемы не изменяется и напряжение на выходе остается неизменным. Однако, если на оба входа действуют напряжения логических 1, то оба транзистора VT2 и VT3 отпираются, их внутреннее сопротивление уменьшается (до 500 - 1000 Ом) и напряжение на выходе Q также становится весьма малым, т. е. на выходе действует логический 0 - в полном соответствии с таблицей истинности И-НЕ (табл. 4.).

|

![]()

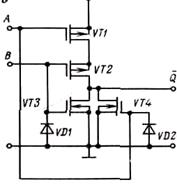

![]() Недостаток схемы - при подаче на входы A и В одновременно напряжений логических 1 схема потребляет ток от источника питания. Если же элемент И-НЕ выполнен на КМОП-транзисторах, то этого не происходит. В частности, на рис. 9, б дается схема подобного элемента. Транзисторы VT1 и VT2 имеют р-каналы, вследствие чего, когда на их затворах (входах A, В) действуют сигналы логических 0, они полностью открыты и на выходе Q имеется положительное напряжение логической 1. При этом транзисторы VT3 и VT4 полностью заперты, ибо имеют n-каналы. Когда на оба входа A, В одновременно действуют положительные напряжения логических 1, транзисторы VT1 и VT2 запираются и напряжение с выхода Q снимается. При этом транзисторы VT3 и VT4 отпираются и выход оказывается соединенным с общим проводом через малое сопротивление (500 - 1000 Ом). Если на одном из входов действует напряжение логического 0, а на другом - напряжение логической 1, то один из транзисторов с р - каналом (VT1 или VT2) запирается, но другой остается открытым, и поскольку они включены параллельно, на выходе остается напряжение логической 1. При этом один из транзисторов с n-каналом (VT3 или VT4) оказывается открытым; другой - закрытым, и, поскольку они включены последовательно, шунтирования выхода Q малым сопротивлением не происходит и напряжение на выходе оказывается высоким. Таким образом, сама схема тока не потребляет (разве что в те мгновения, когда происходит процесс ее переключения — но это, в среднем, доли микроватта). ТТЛ-вариант схемы логического элемента И-НЕ дан на рис. 5, в. Из рассмотрения рисунка вполне очевидно, что схема представляет собой стандартный элемент И (рис. 5, в ), к которому добавлен выходной стандартный усилитель — от инвертора (см. рис. 7, б ). Условные изображения логического элемента И-НЕ дана на рис. 9, г.

Недостаток схемы - при подаче на входы A и В одновременно напряжений логических 1 схема потребляет ток от источника питания. Если же элемент И-НЕ выполнен на КМОП-транзисторах, то этого не происходит. В частности, на рис. 9, б дается схема подобного элемента. Транзисторы VT1 и VT2 имеют р-каналы, вследствие чего, когда на их затворах (входах A, В) действуют сигналы логических 0, они полностью открыты и на выходе Q имеется положительное напряжение логической 1. При этом транзисторы VT3 и VT4 полностью заперты, ибо имеют n-каналы. Когда на оба входа A, В одновременно действуют положительные напряжения логических 1, транзисторы VT1 и VT2 запираются и напряжение с выхода Q снимается. При этом транзисторы VT3 и VT4 отпираются и выход оказывается соединенным с общим проводом через малое сопротивление (500 - 1000 Ом). Если на одном из входов действует напряжение логического 0, а на другом - напряжение логической 1, то один из транзисторов с р - каналом (VT1 или VT2) запирается, но другой остается открытым, и поскольку они включены параллельно, на выходе остается напряжение логической 1. При этом один из транзисторов с n-каналом (VT3 или VT4) оказывается открытым; другой - закрытым, и, поскольку они включены последовательно, шунтирования выхода Q малым сопротивлением не происходит и напряжение на выходе оказывается высоким. Таким образом, сама схема тока не потребляет (разве что в те мгновения, когда происходит процесс ее переключения — но это, в среднем, доли микроватта). ТТЛ-вариант схемы логического элемента И-НЕ дан на рис. 5, в. Из рассмотрения рисунка вполне очевидно, что схема представляет собой стандартный элемент И (рис. 5, в ), к которому добавлен выходной стандартный усилитель — от инвертора (см. рис. 7, б ). Условные изображения логического элемента И-НЕ дана на рис. 9, г.

![]()

Рис. 9. Логический элемент И-НЕ, выполненный на МОП-транзисторах с га-каналами (а), многоэмиттерном биполярном транзисторе и дополнительном усилителе (б), комплементарных МОП-транзисторах (в) и условные графические обозначения элементов ИЛИ-НЕ и И-НЕ в электронных схемах (г)

Логические элементы ИЛИ-НЕ.

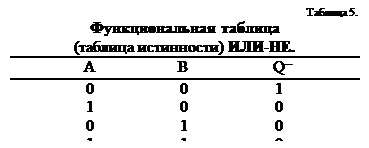

Изменив схему логического элемента ИЛИ на МОП-транзисторах возможно получить новый, более универсальный элемент ИЛИ-НЕ, осуществляющий одновременно с логическим сложением ИЛИ и логическое отрицание (инверсию) НЕ. Для этого активные элементы должны быть использованы не в режиме повторителей (как в схеме рис. 6, б ), а в режиме усилителей-инверторов, что легко достигается перенесением общего сопротивления нагрузки из цепи истоков в цепь стоков. На рис. 10, а приведена такая схема логического элемента ИЛИ-НЕ. При сигналах логического 0 на входах А и В транзисторы VT2 и VT3 заперты, а поскольку транзистор VT1 постоянно открыт и играет роль сопротивления нагрузки, то на выходе Q действует положительное напряжение логической 1. Если на одном из входов А или В (или одновременно на двух) действует положительное, напряжение, соответствующее логической 1, то транзистор VT2 или VT3 или оба вместе оказываются открытыми и напряжение на выходе Q снижается до нескольких десятых долей-единиц вольт, т. е. до уровня напряжения логического 0.

| ||

|

|

Рис. 10. Логические элементы ИЛИ-НЕ, выполненные на биполярных транзисторах (а), МОП-транзисторах с n-каналами (б), комплиментарных парах МОП-транзисторов (в ).

Существенно снизить потребление энергии питания и увеличить быстродействие позволяет использование КМОП-транзисторов. В частности, на рис. 10, б приведена схема такого вида. Транзисторы VT1 и VT2 имеют р-каналы и открываются, если на их затворы подается напряжение логического 0 (так как на их затворы, соединенные с плюсом источника питания, подается отрицательное напряжение в отпирающей полярности). При этом транзисторы VT3 и VT4, имеющие n-каналы, оказываются запертыми и напряжение на выходе Q близко к напряжению источника питания, т. е. к напряжению логической 1. Если хотя бы на одном из входов действует напряжение логической 1, то один из транзисторов VT1 или VT2 закрывается, а поскольку они соединены последовательно, схема отключается от источника питания и на выходе Q напряжение равно 0. В добавление к этому открывается один из транзисторов VT3 или VT4 (включенных параллельно) и выход соединяется с общим проводом через весьма малое сопротивление 100—300 Ом. Таким образом, элемент действует в полном соответствии с таблицей истинности ИЛИ-НЕ (табл. 5.). Следует отметить, что схема чрезвычайно экономична и потребляет ток только в очень краткие мгновения, во время переключения, когда одни транзисторы открываются, а другие еще не успели закрыться.

![]()

![]()

![]()

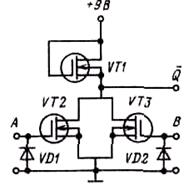

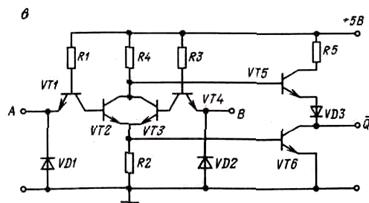

![]() ТТЛ-вариант конструктивного исполнения схемы ИЛИ-НЕ на биполярных транзисторах приведен на рис. 10, в. Из рассмотрения рисунка видно, что схема объединяет в себе двухвходовый элемент ИЛИ (рис. 6, а ) и инвертор НЕ (см. рис. 7, б). Если на входах А и В действуют напряжения логических 0, то переходы база - эмиттер транзисторов VT1 и VT4 открыты и через них протекает ток, минуя переходы база - коллектор. Вследствие этого заперты суммирующие транзисторы VT2 и VT3. Поэтому на базу транзистора VT5 через резистор R4 подается напряжение питания, полностью его отпирающее, в результате чего на выход Q поступает положительное напряжение, соответствующее логической 1. Транзистор VT6, включенный параллельно выходу Q, при этом заперт и тока не проводит, ибо на его базу не подается напряжение (с резистора R2). Если хотя бы на одном из входов А или В действует напряжение логической 1, один из суммирующих транзисторов VT2 или VT3 отпирается, напряжение в точке соединения их коллекторов резко падает, что приводит к запиранию транзистора VT5 и на вход перестает поступать положительное напряжение. При этом оказывается открытым транзистор VT6 шунтирующий своим малым сопротивлением выход, поскольку на его базу начинает подаваться напряжение, снимаемое с резистора R2, включенного в цепь эмиттеров суммирующих транзисторов VT2, VT3 (один из которых проводит ток). Таким образом, схема работает в полном соответствии с табл. 5. Условное изображения логического элемента ИЛИ-НЕ дана на рис. 9, г.

ТТЛ-вариант конструктивного исполнения схемы ИЛИ-НЕ на биполярных транзисторах приведен на рис. 10, в. Из рассмотрения рисунка видно, что схема объединяет в себе двухвходовый элемент ИЛИ (рис. 6, а ) и инвертор НЕ (см. рис. 7, б). Если на входах А и В действуют напряжения логических 0, то переходы база - эмиттер транзисторов VT1 и VT4 открыты и через них протекает ток, минуя переходы база - коллектор. Вследствие этого заперты суммирующие транзисторы VT2 и VT3. Поэтому на базу транзистора VT5 через резистор R4 подается напряжение питания, полностью его отпирающее, в результате чего на выход Q поступает положительное напряжение, соответствующее логической 1. Транзистор VT6, включенный параллельно выходу Q, при этом заперт и тока не проводит, ибо на его базу не подается напряжение (с резистора R2). Если хотя бы на одном из входов А или В действует напряжение логической 1, один из суммирующих транзисторов VT2 или VT3 отпирается, напряжение в точке соединения их коллекторов резко падает, что приводит к запиранию транзистора VT5 и на вход перестает поступать положительное напряжение. При этом оказывается открытым транзистор VT6 шунтирующий своим малым сопротивлением выход, поскольку на его базу начинает подаваться напряжение, снимаемое с резистора R2, включенного в цепь эмиттеров суммирующих транзисторов VT2, VT3 (один из которых проводит ток). Таким образом, схема работает в полном соответствии с табл. 5. Условное изображения логического элемента ИЛИ-НЕ дана на рис. 9, г.

В рассмотренных схемах логических элементов для упрощения показывалось, как правило, лишь два входа. Это совсем не означает, что в реальных схемах их только два - их может быть значительно больше, до 8-10. И есть специальные устройства - расширители, которые позволяют увеличить число входов. Однако в случае необходимости можно увеличить число входов элементов И-НЕ или ИЛИ-НЕ способом наращивания, объединяя последовательно-параллельно несколько отдельных микросхем с меньшим числом входов. При этом может возникнуть проблема: что делать с оставшимися свободными входами? Если применены элементы И в ТТЛ-исполнении, то все свободные входы надо соединить вместе и подключить через резистор в 1 - 2 кОм к плюсу источника питания (+5 В). Свободные входы можно соединить с используемыми, но это не всегда желательно, ибо увеличивается нагрузка на источник сигнала. В МОП и КМОП-схемах И свободные входы можно соединять непосредственно с плюсом источника питания.

Несколько сложнее наращивание в случае элементов ИЛИ-НЕ, И-НЕ, где приходится использовать дополнительные инверторы.

В современной цифровой технике в настоящее время доминируют четыре семейства логических микросхем в интегральном исполнении: ТТЛ; ТТЛШ; КМОП и ЭСЛ, выпускаемые во всем мире сотнями миллионов штук ежегодно. При этом наиболее широко применяются для построения цифровых информационно-измерительных геофизических устройств микросхемы ТТЛ, ТТЛШ и КМОП. Цифровые микросхемы семейства ЭСЛ, пока не имеющие себе равных по быстродействию (доли наносекунды), потребляют слишком много энергии питания и используются преимущественно для создания сверхбыстродействующих ЭВМ универсального применения.

Все логические элементы выпускаются в виде микросхем в интегральном исполнении и маркируются стандартным семиэлементным кодом. При этом третий элемент маркировки — две буквы — обозначает: ЛИ — элемент И; ЛН — элемент НЕ; ЛЛ — элемент ИЛИ; ЛА — элемент И-НЕ; ЛЕ — элемент ИЛИ-НЕ; ЛС — элемент И-ИЛИ; ЛБ — элемент И-НЕ/ИЛИ-НЕ; ЛР — элемент И-ИЛИ-НЕ; Л К — элемент И-ИЛИ-НЕ/И-ИЛИ; ЛМ— элемент ИЛИ-НЕ/ИЛИ; ЛД — расширители; ЛП — прочие типы элементов (в том числе исключающее ИЛИ); ХЛ — многофункциональные элементы.

Список использованной литературы

1. Бобровников Л. З. Радиотехника и электроника. М. Недра, 1990 г.

2. Гутников В. С. Интегральная электроника в измерительных приборах. Л. Энергия, 1978 г.

3. Ямпольский В. С. Основы автоматики и вычислительной техники. М. Просвещение, 1991 г.

4. Нефёдов В. И. Основы радиоэлектроники. М. Высшая школа, 1994 г.