Реферат: Стенд проверки устройства контроля свободности железнодорожного перегона

![]()

![]()

![]()

![]() 3 4

3 4

1 ![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

5 6 2 +15V СРП

![]()

![]()

![]()

![]()

![]() 1 3

1 3

![]()

![]()

9 1 8

11 1 10

![]()

![]() 13 1 12

13 1 12

![]()

Рис.4.3 Формирование сигнала ИВ

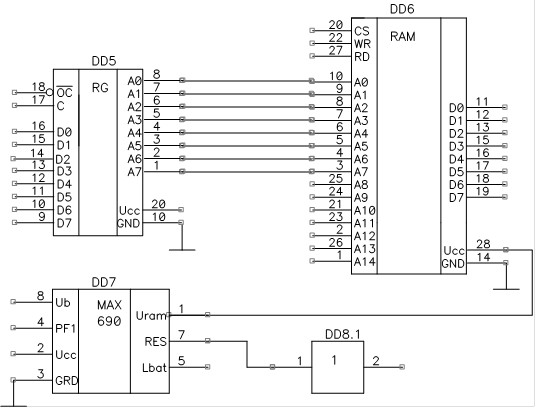

Рис.4.4 Организация внешней памяти

Для передачи данных на порт Р0 микроконтроллера предназначен восьмиразрядный магистральный передатчик DD10 без инверсии входной информации КР1533АП14, приведенный на рис.4.5.

![]()

![]()

![]() DD9

DD9

![]() DD10

DD10

![]()

![]()

![]()

![]()

![]()

![]()

![]() К СРП 1 2

К СРП 1 2 ![]()

![]()

![]()

![]() 2 D1/0 DS D0.0 3

2 D1/0 DS D0.0 3

![]()

![]()

![]()

![]()

![]()

![]() SA1 4 D1.1 D0.1 5

SA1 4 D1.1 D0.1 5

![]()

![]() 6 D1.2 D0.2 7

6 D1.2 D0.2 7

![]() SB1 8 D1.3 D0.3 9

SB1 8 D1.3 D0.3 9

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]() +5V SB2 12 D1.4 D0.4 11

+5V SB2 12 D1.4 D0.4 11

![]()

![]()

![]()

![]()

![]()

![]()

![]() SB3 14 D1.5 D0.5 13

SB3 14 D1.5 D0.5 13

BUSY

![]()

![]() 16 D1.6 D0.6 15

16 D1.6 D0.6 15

RD 18 D1.7 D0.7 17

![]()

![]()

![]()

![]()

![]()

![]()

![]() 1 CO1 Ucc 20 +5V

1 CO1 Ucc 20 +5V

![]() DD8.2

DD8.2