Реферат: Структурная схема ЭВМ

3.2 Образование дополнительного кода.

Дополнительный код образуется из прямого кода инверсией и добавлением единицы к младшему разряду. Если результат получился отрицательным, то чтобы получить прямой код необходимо осуществить инверсию, а затем добавить единицу к младшему разряду. Единица переполнения знакового разряда при использовании дополнительного кода отбрасывается.

4. УЗЛЫ ЭВМ.

Узлы ЭВМ классифицируются на :

1. комбинационные - это узлы, выходные сигналы которых определяются только сигналом на входе, действующим в настоящий момент времени (дешифратор). Выходной сигнал дешифратора зависит только от двоичного кода, поданного на вход в настоящий момент времени. Комбинационные узлы называют также автоматами без памяти.

2. последовательностные (автоматы с памятью) - это узлы, выходной сигнал которых зависит не только от комбинации входных. сигналов, действующих в настоящий момент времени, но и от предыдущего состояния узла (счетчик).

3. программируемые узлы функционируют в зависимости от того, какая программа в них записана. Например, программируемая логическая матрица (ПЛМ), которая в зависимости от прожженной в ней программы может выполнять функции сумматора, дешифратора, ПЗУ.

5. СУММАТОР

|

|

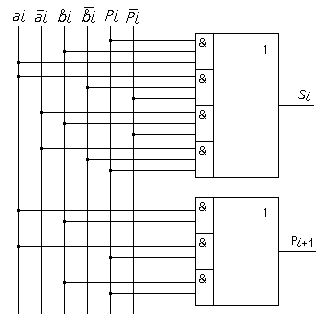

Сумматор может быть построен как комбинационная схема -

последовательный сумматор и как

последовательностная схема -

накапливающий сумматор. Сумматор осуществляет cуммирование цифр разрядов слагаемых и цифр переноса по правилам сложения по модулю 2. Работа сумматора строго регламентирована в соответствии с таблицей:

| ai | bi | Pi | Si | Pi+1 |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

6. ПОСЛЕДОВАТЕЛЬНЫЙ СУММАТОР

|

|

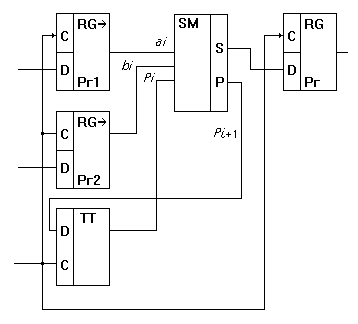

Последовательный сумматор осуществляет суммирование слагаемых и цифр переноса поразрядно, начиная с младшего разряда. Основой его схемы является одноразрядный сумматор. Суммирование производится в одноразрядном сумматоре SM. Цифры i-того разряда слагаемого и цифра переноса из младшего разряда передаются на вход сумматора одновременно с приходом тактового импульса. Регистры 1 и 2 используются для приема и хранения цифр i-того разряда слагаемых. В D - триггере хранится цифра переноса из младшего разряда. Регистр 3 принимает и хранит цифру i-того суммы. С приходом тактового импульса из регистров 1, 2 и D - триггера разряда слагаемых и цифра переноса поступает на вход одноразрядного сумматора. Одновременно регистр 3 освобождается для приема цифры суммы.

|

|

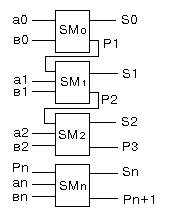

В параллельном сумматоре все разряды операндов суммируются одновременно, но быстродействие снижается за счет времени передачи цифры переноса из младшего разряда.

7. АРИФМЕТИКО - ЛОГИЧЕСКОЕ УСТРОЙСТВО (АЛУ)

АЛУ предназначено для выполнения арифметических и логических операций над операндами. АЛУ классифицируются следующим образом:

1. По способу действий над операндами. Бывают АЛУ последовательного и параллельного действия. В последовательных АЛУ действия над операндами производятся последовательно разряд за разрядом начиная с младшего. В параллельных АЛУ все разряды операндов обрабатываются одновременно.

2. По виду обрабатываемых чисел АЛУ могут производить операции над двоичными числами с фиксированной или плавающей запятой и над двоично- десятичными числами.

Каждая десятичная цифра записывается четырьмя разрядами двоичного кода.

1971

0001 1001 0111 0001

АЛУ при действии над двоично-десятичными числами должны содержать схему десятичной коррекции. Схема десятичной коррекции преобразует полученный результат таким образом, чтобы каждый двоично-десятичный разряд не содержал цифру больше 9.

При записи числа с фиксированной запятой запятая фиксируется после младшего разряда, если число целое, и перед старшим, если число меньше 1.

При записи чисел с плавающей запятой выделяется целая часть, которая называется мантиссой, и показатель степени, который характеризует положение запятой.

37 и 0.37 - с фиксированной запятой

37*10^-2 - с плавающей запятой