Реферат: Структурная схема ЭВМ

В блочных АЛУ отдельные блоки предназначены для действий над двоично-десятичными числами, отдельно для действий над числами с фиксированной запятой, отдельно с плавающей запятой.

В многофункциональных АЛУ одни и те же блоки обрабатывают числа с фиксированной запятой, плавающей запятой и двоично-десятичные числа.

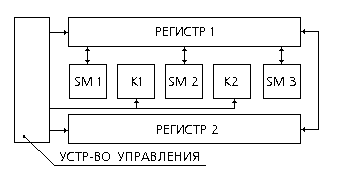

Многофункциональное АЛУ

|

|

Клапаны К1 и К2 объединяют сумматоры 1,2 и 3 для действий над числами с фиксированной запятой.

Для действий над числами с плавающей запятой клапан К2 объединяет сумматоры 2 и 3 для обработки мантисс, а клапан К1 отсоединяет первый сумматор от второго. Сумматор 1 обрабатывает порядки.

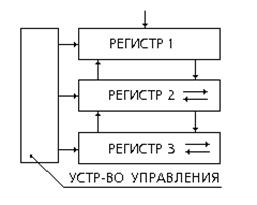

4. По структуре АЛУ бывают с непосредственными связями и многосвязными. АЛУ с непосредственной связью В многосвязных АЛУ входы и выходы регистров приемников и источников информации подсоединяются к одной шине. Распределение входных и выходных сигналов происходит под действием управляющих сигналов.

|

|

В АЛУ с непосредственной связью вход регистра приемника связан с выходом регистра источника операндов и регистра, в котором происходит обработка.

Например, в этой схеме суммирование происходит так: операнды подаются в регистр 1. Регистр 2 является накапливающим сумматором или автоматом с памятью. Он суммирует слагаемые, поступающие в разные моменты времени и передает результат в регистр 3.

Умножение в этом АЛУ происходит так: множимое помещают в регистр 4, множитель - в регистр 1. Регистры 2 и 3 являются кроме того сдвигающими

регистрами. В зависимости от содержимого разряда множителя, множимое сдвигается на один разряд, если множитель содержит 1, и на два, если множитель содержит 0. Эти частные произведения суммируются в регистре 2.

8. ДЕШИФРАТОР

Дешифратор предназначен для преобразования двоичного кода на входе в управляющий сигнал на одном из выходов. Если входов n то выходных шин должно быть N = 2^n.

| X1 | X2 | X3 | Z0 | Z1 | Z2 | Z3 | Z4 | Z5 | Z6 | Z7 |

| 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

В зависимости от количества разрядов входного числа и от количества входов элементов, на которых построен дешифратор. Дешифраторы могут быть линейные, у которых все переменные Х1, Х2, Х3 подаются на вход одновременно.

|

|

Их быстродействие больше, но более 3-х переменных одновременно подать нельзя, поэтому чаще применяются многокаскадные дешифраторы. Количество элементов в каждом следующем разряде больше, чем в предыдущем.

На вход первого каскада подается один слог, на вход следующего каскада второй слог и результаты коньюнкций, произведенных в первом каскаде.

Простейший линейный дешифратор можно построить на диодной матрице:

В этой схеме используется отрицательная логика. При подаче "1" на анод диода он закрывается. Если закрыты все 3 диода, подсоединенные к одной гориз. линии то на этой линии потенциал -Е, соответствующий уровню "1".

Многокаскадный дешифратор можно организовать вот таким образом:

|

|

Два линейных дешифратора обрабатывают по 2 слова. В последнем каскаде образуются конъюнкции вых. сигнала первого каскада. Многокаскадные дешифраторы обладают меньшим быстродействием.

9. ПРЕОБРАЗОВАТЕЛИ С ЦИФРОВОЙ ИНДИКАЦИЕЙ

Схема устроена так, что управляющий. сигнал = 1 гасит соответствующий элемент Z (Zn соотв Yn). Преобразователь работает в соответствии с таблицей:

|

деся-тичн. | "8421" | cостояние эл-тов Z1-Z7 (Y1 - Y7) | ||||||||||

|

| X4 | X3 | X2 | X1 | Y1 | Y2 | Y3 | Y4 | Y5 | Y6 | Y7 | |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | |

| 1 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | |

| 2 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | |

| 3 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | |

| 4 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | |

| 5 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | |

| 6 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | |

| 7 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | |

| 8 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |

| 9 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | |

Схема преобразователя с цифровой индикацией :

10. ПРЕОБРАЗОВАТЕЛЬ КОДА 8421 В 2421

|

|

Код 2421 образуется из кода 8421. До 4-х он повторяет код 8421, а дальше образуется как инверсия дополнения до 9-и. Код 8421 является двоично-десятичным кодом, где коэффициенты 8,4,2 и 1 являются весовыми коэффициентами, т.е. соответствуют "стоимости" каждого разряда. Сочетания: 1010, 1011, 1100, 1101, 1110, 1111