Реферат: Выборочные ответы к государственному экзамену факультета ВМС специальности 2201

Билет №17 вопрос №1

Структура и компоновка ОЗУ основных моделей СМ ЭВМ.

Данный вопрос рассмотрим на примере модулей памяти модели СМ 1810. Модуль оперативный запоминающий МОЗ 256 СМ. Он предназначен для приема, хранения и выдачи оперативной информации в качестве встроенной оперативной памяти в составе микроЭВМ СМ 1810. Модуль имеет следующие технические характеристики:

Объем – 256 Кб

Разрядность – 8 и 16 бит

Порядок обращения – произвольный

Выполняемые операции – запись слова (ЗПС), чтение слова (ЧТС), запись байта (ЗПБ), чтение байта (ЧТБ)

Цикл обращения – при операциях ЧТС, ЗПС, ЧТБ не более 0,7 мкс, при операции ЗПБ не более 1,4 мкс

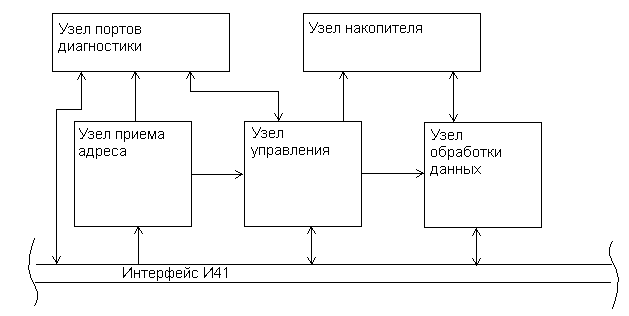

Модуль обеспечивает коррекцию одинарной и обнаружение двойной ошибки. На рис. показана структурная схема модуля. Узел приема осуществляет формирование адреса обращения к требуемой ячейке памяти при обращении к модулю со стороны интерфейса И41, узел обработки данных осуществляет прием и выдачу данных на (из) интерфейса И41. В его состав входит корректор, обеспечивающий при операциях записи формирование контрольных разрядов накопителя. При операциях чтения корректор формирует признаки одинарной и двойной ошибки и в случае одинарной ошибки производит коррекцию данных и выдачу их через соответствующий буферы на интерфейс И41. Узел управления формирует сигналы управления другими узлами модуля и соответствующую диаграмму. В его состав входит контроллер памяти КМ1810ВТ03, осуществляющий формирование управляющих сигналов для динамических микросхем памяти, прием и мультиплексирование адресов строки и столбца, а также формирует режим регенерации.

Узел накопителя предназначен для записи, хранения и выдачи информации представляет собой матрицу микросхем памяти К565РУ5 (64К х 1). Матрица содержит два ряда по 22 микросхемы. Разряд данных включает в себя по одной микросхеме из каждого ряда; таким образом, в матрице всего по 16 информационных и 6 контрольных разрядов. Полная емкость накопителя 128К х 22 бит, где К=1024бит

Узел портов диагностики осуществляет прием и выдачу информации о диагностики модуля и состоит из портов ввода-вывода, в которых хранится информация о работоспособности модуля.

В состав СМ1810 входит еще один модуль оперативной памяти МОЗ 4М, который отличается от МОЗ256 большей емкостью (до 4 Мбайт). Остальные параметры МОЗ 4М аналогичны МОЗ 256. МОЗ 4М состоит из пяти плат, которые устанавливаются в соответствующие места 1810.40 и 1810.41. Из них одна плата выполняет функции контороллера памяти, остальные четыре платы – функции накопителя. Платы накопителя полностью взаимозаменяемы и служад для наращивания накопителя блоками по 1 Мбайт до 4х. Минимальная емкость МОЗ 4М – 1 Мбайт.

Билет №3 вопрос №1

Общая характеристика микропроцессора. Функции и структурная схема МП.

Развитие технологии и схемотехники БИС привело к появлению в середине 70 – х годов нового типа интегрального электронного прибора, представляющего собой функционально законченное устройство обработки цифровой информации, управляемое хранимой в памяти программой и конструктивно выполненного в виде одного или нескольких БИС и СБИС. Такой прибор получил название микропроцессора, так как по своим логическим функциям и структуре напоминает упрощенный вариант процессора обычных ЭВМ, а именно дешифрация и выполнения команд микропрограммы, организация обращения к оперативной памяти, в нужных случаях инициирование работы каналов и периферийных устройств, восприятие и обработка запросов, поступающих из устройств машины и внешней среды. По выполняемым функциям микропроцессор является центральной частью объекта, управляющим взаимодействием ее устройств. Отличия от процессора можно сформулировать следующим образом: - меньшая разрядность обрабатываемых данных, меньшая точность вычислений;

-

упрощенная система арифметико-логических команд;

-

меньшими объемами прямоадресуемой памяти, выполнением операций адресной арифметики операций по обмену данными с внешними устройствами с помощью одного и того же АЛУ, надо отменить, что перспективные модели МП лишены этих отличий.

Структурная схема микропроцессора.

Основными особенностями организации современных микропроцессоров и микро-ЭВМ является:

А) Модульная структура, в которой модули являются функционально законченными устройствами

Б) Магистральная организация связей между модулями, при которой общие шины используются разными модулями

В) Микропрограммное управление

Г) Байтовая адресация памяти и побайтовая обработка данных

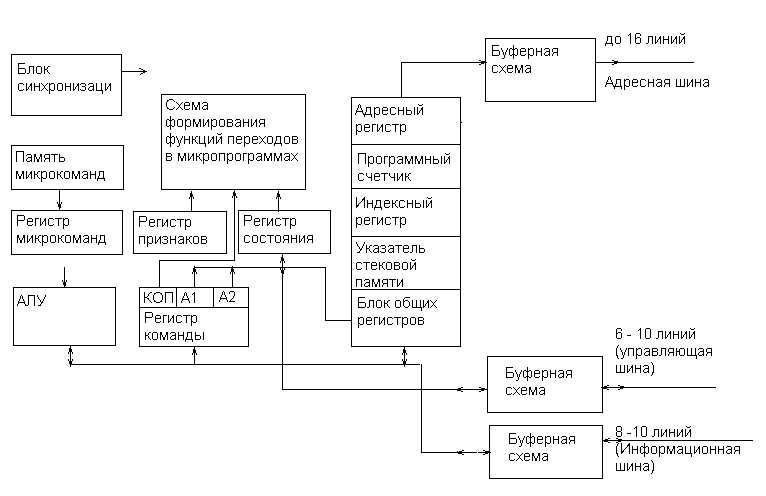

Д) Использование внутренних сверхоперативных регистров, см. Рис

В структуре можно выделить три основные части: центральный процессор, блок управления и постоянная память микропрограмм. Центральный процессор содержит АЛУ, сверхоперативную память в виде программно доступных общих регистров и функциональные регистры – командный, индексный, адресный, указатель стека и программный счетчик. АЛУ состоит из двоичного сумматора, сдвигающего регистра, двух регистров операндов и регистра результата. Схемы АЛУ выполняют команды сложения, вычитания, логическое И, ИЛИ, сложение по модулю 2 и сдвигов. Более сложные операции реализуются программно. Блок микропрограммного управления содержит дешифратор кода операции, схему формирования функций перехода к следующему адресу в микропрограмме и регистр адреса микрокоманды. Система прерывания в микропроцессорах достаточно проста и предназначена только для восприятия прерываний от внешних источников. Микропроцессоры имеют упрощенные схемы управления ПУ. В значительной степени управление этими устройствами реализуется посредством микропрограммного управления. Блок постоянной памяти микропрограмм, реализующих команды микропроцессора, обычно выполняется в виде отдельной БИС. В микропроцессорах используют косвенную, непосредственную, индексную адресации основной оперативной памяти и прямую адресацию общих регистров. Сверхоперативная память на общих регистрах, позволяет сократить количество обращений к внешней памяти и уменьшить необходимое количество выводов корпуса за счет сокращения формата команды. Из-за ограниченного числа выводов корпуса БИС не удается реализовать интерфейс микропроцессора с высокой пропускной способностью. Поэтому микропроцессоры имеют так называемый общий интерфейс, обслуживающий как внешнюю оперативную память, так и ПУ. Если не удается выделить для интерфейса достаточное количество выводов, применяют мультиплексирование шин (использование шин для разных целей на основе разделения времени). Для обеспечения совместной работы микропроцессора и внешнего оборудования шины интерфейса снабжаются буферными схемами, в которых используются электронные схемы с тремя состояниями и спец. линии управления выдачи данных.

Билет №4 вопрос №1

Классификация вычислительных устройств, аналоговые и цифровые вычислительные устройства.

--> ЧИТАТЬ ПОЛНОСТЬЮ <--