Шпаргалка: Задачи по схемотехнике

Перевести следующие числа из десятичной системы счисления в двоичную и из двоичной в шестнадцатеричную: 127,184,356,200,427.

127=128-1 = 1111111;

0111|1111= 7FH;

184=128+32+16+8=10111000;

1011|1000=B8H;

356=256+64+32+4=101100100;

1|0110|0100=164H;

200=128+64+8=11001000;

1100|1000=C8H;

427=256+128+32+8+2+1=110101011;

1|1010|1011=1ABH;

1.2. Перевести следующие числа из шестнадцатеричной системы в двоичную и из двоичной в десятичную, а также непосредственно из шестнадцатеричной в десятеричную: BD5H; 8E1H; CABH; 91DH; AF1H;

BD5H=1011|1101|0101=1+4+16+64+128+256+512+2048=3029;

162*11+162*13+160+5=3029;

8E1H=1000|1110|0001=1+32+64+128+2048=2273;

8E1H=8*162+4*161+1*160=2273;

CABH=110010101011=1+2+8+32+128+1024+2048=3243;

CABH=12*162+10*161+11=3243;

91DH=100100011101=1+4+8+16+256+2048=2333;

91DH=9*162+1*16+13=2333;

AF1H=101011110001=1+16+32+64+128+512+2048=2801;

AF1H=162*10+16*15+1=2801;

1.4. На вход узла равнозначности подается серия импульсов, приведенная на рис.1.2. Построить временную диаграмму выходного сигнала без учета задержек и фронтов, создаваемых логическими элементами устройства.

|

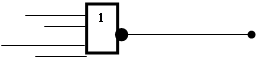

1.6. Синтезировать шифратор на пять входов

а) на элементах ИЛИ-НЕ;

б) на элементах И-НЕ;

|

|

![]()

![]()

![]()

![]()

![]() b

b

![]()

![]()

|

|

![]()

![]()

![]() e

e

| |

| |

--> ЧИТАТЬ ПОЛНОСТЬЮ <--