Учебное пособие: Мікроконтролери CISC архітектури

Однак, гарвардська архітектура є недостатньо гнучкою для реалізації деяких програмних процедур. Тому порівняння МК, виконаних на основі різних архітектур, варто проводити стосовно до конкретних задач.

МК звичайно класифікують по розрядності оброблюваних чисел:

- чотирирозрядні – найпростіші і найдешевші;

- восьмирозрядні – найбільш чисельна група, що забезпечує оптимальне співвідношення вартості і можливостей; до цієї групи відносяться МК серії MCS-51 (Intel) і сумісні з ними, PIC (MicroChip), HC68 (Motorola), Z8 (Zilog) та ін.;

- шістнадцатирозрядні – MCS-96 (Іntel) та ін. – більш високопродуктивні;

- тридцатидворозрядні – звичайно є модифікаціями універсальних мікропроцесорів, використовуються для вирішення найбільш складних задач (наприклад, адаптивного керування).

Найбільш розповсюджені у дійсний час восьмирозрядні ОМК, широко використовувані в промисловості, побутовій і комп'ютерній техніці. Причиною життєздатності 8-розрядних МК є використання їх для керування реальними об'єктами, де застосовуються, в основному, алгоритми з переважно логічними (побітовими) операціями, швидкість виконання яких практично не залежить від розрядності процесора.

Сучасні 8-розрядні МК мають наступні особливості:

- модульна організація , при якій на базі одного процесорного ядра проектується ряд (лінійка) МК, що розрізняються обсягом і типом пам'яті програм, обсягом пам'яті даних, набором периферійних модулів, частотою синхронізації;

- використання закритої архітектури МК . Тобто МК являє собою закінчену систему обробки даних, нарощування можливостей якої з використанням паралельних магістралей адреси і даних не передбачається;

- використання типових функціональних периферійних модулів (таймери, процесори подій, контролери послідовних інтерфейсів, АЦП й ін.), що мають незначні відмінності в алгоритмах роботи в МК різних виробників;

- декілька режимів функціонування периферійних модулів , що задаються в процесі ініціалізації регістрів спеціальних функцій МК.

1.2. Типова структура модульного МК

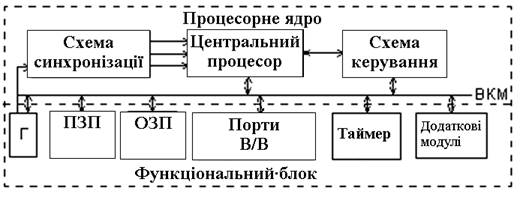

При модульному принципі побудови всі МК одного сімейства містять процесорне ядро, однакове для всіх МК даного сімейства, і змінюваний функціональний блок, що відрізняє МК різних моделей. Структура модульного МК подана на рис. 1.

Процесорне ядро містить у собі:

· центральний процесор;

· внутрішню контролерную магістраль (ВКМ) у складі шин адреси, даних і керування;

· схему синхронізації МК;

· схему керування режимами роботи МК.

Змінюваний функціональний блок містить у собі модулі пам'яті різного типу й обсягу, порти введення/виведення, модулі тактових генераторів (Г), таймери. У відносно простих МК модуль обробки переривань входить до складу процесорного ядра. У більш складних МК він являє собою окремий модуль з розвиненими можливостями. До складу змінюваного функціонального блоку можуть входити і такі додаткові модулі, як компаратори напруги, АЦП і інші. Кожен модуль проектується для роботи в складі МК з урахуванням протоколу ВКМ. Даний підхід дозволяє створювати різноманітні МК у межах одного сімейства.

Процесорне ядро сучасних 8-розрядних МК може бути побудовано на основі CISC- архітектури (повна система команд -- Complicated Instruction Set Computer ), або RISC -архітектури (скорочена система команд -- Reduced Instruction Set Computer ).

CISC -процесори виконують великий набір різноманітних команд, даючи розроблювачеві можливість вибрати найбільше підходящу команду для виконання необхідної операції. Вибірка команди на виконання здійснюється побайтно протягом декількох циклів роботи МК. Час виконання команди може складати від 1 до 12 циклів. До МК із CISC -архітектурою відносяться МК фірми Intel з ядром MCS-51 , що підтримуються в даний час великою кількістю виробників.

Схема синхронізації МК забезпечує формування сигналів синхронізації, необхідних для виконання командних циклів центрального процесора та мітки часу, які необхідні для роботи таймерів МК. Вона звичайно будується на основі дільників частоти опорної імпульсної послідовності. Сучасні МК містять вбудовані тактові генератори, але практично всі МК допускають роботу від зовнішнього джерела сигналу з метою завдання довільної тактової частоти МК.

У МК використовується три основних види пам'яті:

Пам'ять програм являє собою ПЗП, призначену для збереження програм і констант.

Пам'ять даних призначена для збереження змінних у процесі виконання програми і являє собою, як правило, статичне ОЗП. Термін «статичне» означає, що вміст комірок ОЗП зберігається при зниженні тактової частоти МК до як завгодно малих значень.

Регістри МК – внутрішні регістри процесора (акумулятор, регістри стану, індексні регістри) і регістри, що служать для керування периферійними пристроями (регістри спеціальних функцій).

Обсяг пам'яті данихМК, як правило, невеликий і складає звичайно десятки і сотні байт. Цю обставину необхідно враховувати при розробці програм для МК.

Незважаючи на існуючу тенденцію переходу до закритої архітектури МК, у деяких випадках виникає необхідність підключення додаткової зовнішньої пам'яті . Для цього використовуються порти введення-виведення. Такий спосіб дозволяє уникнути реалізації складних шинних інтерфейсів, однак приводить до зниження швидкодії системи при звертанні до зовнішньої пам'яті.

Кожен МК має декілька паралельних портів введення-виведення, які виконують роль пристроїв часового узгодження функціонування МК і об'єкта керування, що у загальному випадку працюють асинхронно. Звертання до регістра даних порту здійснюється тими ж командами, що і звертання до пам'яті даних. Крім того, у багатьох МК окремі розряди портів можуть бути опитані або встановлені бітовими командами процесора.