Учебное пособие: Мікроконтролери CISC архітектури

Покладати функції керування в реальному масштабі часу тільки на центральний процесор неефективно, тому що це займає ресурси, необхідні для розрахункових процедур. Тому в більшості сучасних МК використовується апаратна підтримка роботи в реальному часі з використанням таймерів .

Модулі таймерів служать для прийому інформації про час настання тих або інших подій від зовнішніх датчиків подій, а також для формування керуючих впливів у часі. Таймер – це 8-ми або 16-розрядний лічильник зі схемою керування. Схемотехнікою МК передбачається можливість використання таймера в режимі лічильника зовнішніх подій, тому його часто називають таймером/лічильником. Напрямок рахування – тільки прямий, тобто при надходженні вхідних імпульсів вміст лічильника інкрементується (збільшується на одиницю).

Лічильник може використовувати, у якості джерела вхідних сигналів як імпульсну послідовність з виходу керованого дільника частоти fBUS , так і сигнали зовнішніх подій. У першому випадку говорять, що лічильник працює в режимі таймера, у другому – у режимі лічильника подій.

Наступним етапом розвитку модулів підсистеми реального часу МК стали модулі процесорів подій. Вперше модулі процесорів подій були використані компанією Intel у МК сімейства 8x51Fx. Цей модуль одержав назву програмувального лічильного масиву (Programmable Counter Array — PCA). Він забезпечує більш широкі можливості роботи в реальному масштабі часу і меньше витрачає ресурси центрального процесора, чим таймери/лічильники. Тенденція розвитку підсистеми реального часу сучасних МК – збільшення числа каналів процесорів подій і розширенні їхніх функціональних можливостей.

Обробка переривань у МК відбувається відповідно до загальних принципів обробки переривань у МПС. Модуль переривань приймає запит переривання і організує перехід до виконання програми, що перериває. Запити переривань можуть надходити як від зовнішніх джерел, так і від джерел, розташованих у різних внутрішніх модулях МК (зовнішні та внутрішні переривання). Як входи для прийому запитів зовнішніх переривань найчастіше використовуються виводи паралельних портів.

Адреса, що завантажується в програмний лічильник при переході до обробки переривання, називається «вектор переривання». Питання про пріоритети при одночасному надходженні декількох запитів на переривання вирішується в різних МК по-різному. Є МК з однорівневою системою пріоритетів (усі запити рівноцінні), багаторівневою системою з фіксованими пріоритетами і багаторівневою програмованою системою пріоритетів .

Сучасні МК надають користувачеві великі можливості в плані економії енергоспоживання і мають наступні режими роботи:

- активний режим (Run mode) — основний режим роботи МК. У цьому режимі МК виконує робочу програму, і всі його ресурси доступні. Споживана потужність має максимальне значення PRUN .

- режим очікування (Wait mode, Idle mode або Halt mode). У цьому режимі припиняє роботу центральний процесор, але продовжують функціонувати периферійні модулі, що контролюють стан об'єкта керування. При необхідності сигнали від периферійних модулів переводять МК в активний режим, і робоча програма формує необхідні керуючі впливи. У режимі очікування потужність споживання МК знижується в порівнянні з активним режимом у 5...10 разів;

- режим останова (Stop mode, Sleep mode або Power Down mode). У цьому режимі припиняє роботу як центральний процесор, так і більшість периферійних модулів. Перехід МК зі стану останова в робочий режим можливий, як правило, тільки за перериваннями від зовнішніх джерел або після подачі сигналу скидання. У режимі останова потужність споживання МК PSTOP знижується в порівнянні з активним режимом приблизно на три порядки і складає одиниці мікроват.

З метою забезпечення надійного запуску, контролю роботи МК і відновлення працездатності системи (автоматічного скидання і ініціалізації) всі сучасні МК забезпечуються апаратними засобами забезпечення надійної роботи, а саме: схемою формування сигналу скидання МК, модулем моніторингу напруги живлення та сторожовим таймером.

2. Базова архітектура CISC МК.

В дійсний час, серед усіх 8-розрядних МК, сімейство MCS51 є безсумнівним чемпіоном з кількості різновидів і кількості компаній, що випускають його модифікації. Воно одержало свою назву від першого представника цього сімейства -- МК і8051 , випущеного в 1980. Вдалий набір периферійних пристроїв, можливість гнучкого вибору зовнішньої або внутрішньої програмної пам'яті і невисока вартість забезпечили цьому МК успіх на ринку. З погляду технології МК і8051 був для свого часу дуже складним виробом -- у кристалі було використано 128 тис. транзисторів, що в 4 рази перевищувало кількість транзисторів у 16-розрядному мікропроцесорі 8086.

Важливу роль у досягненні такої високої популярності сімейства 8051 зіграла відкрита політика фірми Intel, спрямована на широке поширення ліцензій на ядро 8051 серед великої кількості провідних компаній - виробників світу.

У результаті на сьогоднішній день існує більш 200 модифікацій МК сімейства 8051, що випускаються майже 20-ю компаніями. Ці модифікації містять у собі кристали з найширшим спектром периферії: від простих 20-вивідних пристроїв з одним таймером до 100-вивідних кристалів з 10-розрядними АЦП, масивами таймерів-лічильників, апаратними 16-розрядними помножувачами і 64 Кб програмної пам'яті на кристалі. Основними напрямками розвитку є: збільшення швидкодії (підвищення тактової частоти і вдосконалення архітектури), збільшення обсягу ОЗП і FLASH - пам'яті на кристалі з можливістю внутрісхемного програмування, використання складних периферійних пристроїв.

Усі МК із сімейства MCS-51 мають загальну систему команд. Наявність додаткового устаткування впливає тільки на кількість регістрів спеціального призначення.

Склад та основні характеристики базової моделі сімейства МК MCS-51

Базовою моделлю сімейства МК MCS51 і основою для всіх наступних модифікацій є МК і8051 . Це -- восьмирозрядний ОМК, що має:

- вбудований тактовий генератор;

- адресний простір пам'яті програм -- 64 КБ;

- адресний простір пам'яті даних -- 64 КБ;

- внутрішню (резидентну) пам'ять програм ПЗП -- 4 КБ;

- внутрішню (резидентну) пам'ять даних ОЗП -- 128 байт;

- додаткові можливості по виконанню операцій булевої алгебри (побітових операції);

- 32 двонапрямлені й індивідуально адресовані лінії введення/виведення (порти Р0-Р3 );

- послідовний порт (Serial Port);

- 2 шістнадцатирозрядні багатофункціональні таймери/лічильники (Т/С 0, Т/С 1 );

- повнодуплексний асинхронний прийомопередавач;

- векторну систему переривань із двома рівнями пріоритету і шістьма джерелами подій.

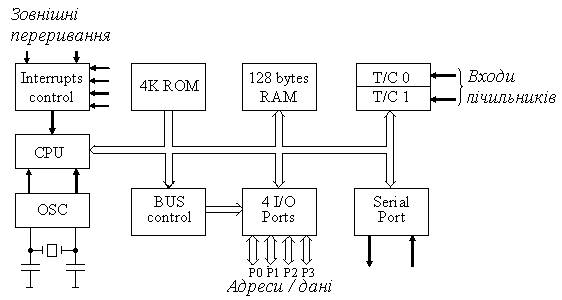

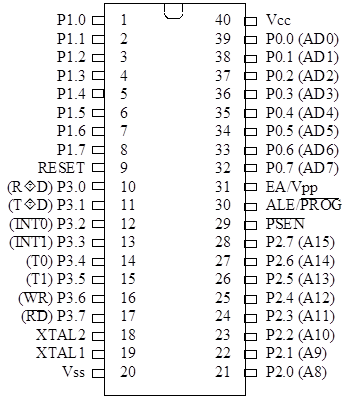

Спрощена структурна схема і8051 подана на рис. 2, призначення виводів мікросхеми -- на рис. 3.

Рис. 2. Структурна схема і8051

Bus control –блок керування; Interrupts control – система переривань; CPU – центральний процесор; OSC – генератор; ROM –ПЗП; RAM – ОЗП; I/O ports – порти введення-виведення.

Рис. 3. Призначення виводів I-8051.