Учебное пособие: Мікроконтролери CISC архітектури

· Uss -- потенціал загального проводу ("землі");

· Ucc -- основна напруга живлення +5 В;

· XTAL1, XTAL2 -- виводи для підключення кварцового резонатора;

· RESET -- вхід загального скидання МК;

· PSEN -- дозвіл зовнішньої пам'яті програм;

· ALE -- строб адреси зовнішньої пам'яті;

· ЕА -- відключення внутрішньої програмної пам'яті;

· P1 -- восьмибітний квазідвонапрямлений порт введення/виведення (кожен розряд порту може бути запрограмований як на введення, так і на виведення інформації);

· P2 -- порт, аналогічний Р1 ; крім того, виводи цього порту використовуються для видачі адресної інформації при звертанні до зовнішньої пам'яті програм або даних;

· РЗ -- аналогічний Р1 ; крім того, виводи цього порту можуть виконувати ряд альтернативних функцій, що використовуються при роботі таймерів, порту послідовного введення/виведення, контролера переривань, і зовнішньої пам'яті програм і даних;

· P0 — восьмибітний двонапрямлений порт введення/виведення інформації.

2.2. Організація пам’яті базової моделі сімейства МК MCS-51

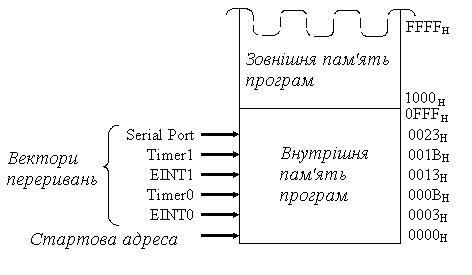

Вся серія MCS51 має гарвардську архітектуру (пам'ять даних відділена від пам'яті програм). Організація резидентної пам'яті програм (РПП) зображена на рис. 4.

Область нижніх адрес РПП використовується системою переривань, забезпечена підтримка п'яти джерел переривань -- двох зовнішніх (EINT1 та EINT1) , двох переривань від таймерів та одного від послідовного порту. Молодша адреса ПЗП використовується для початку роботи ОМК після скидання сигналом RESET.

Пам'ять програм може бути розширена до 64 кБайт через приєднання зовнішніх ВІС ПЗП.

Рис. 4. Організація РПП

ОЗП або резидентна пам'ять даних (РПД) складається з двох областей. Перша область – ОЗП даних із інформаційній ємністю 128*8 біт з адресами 0 -- 7FH. Друга область – регістри спеціальних функцій SFR (Special Function Register) з адресами 80Н – FFH. РПД.

2.3. Регістри МК MCS-51

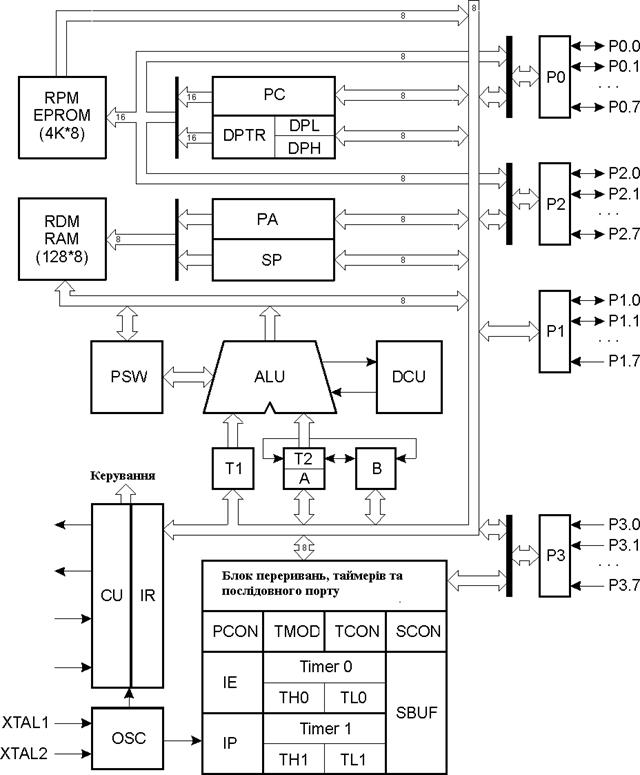

Структурна схема МК MCS-51 , деталізована до регістрів, подана на рис.5. Розглянемо склад схеми та призначення її елементів.

Блок ЦП містить 8-розрядний АЛП (ALU) зі схемою десяткової корекції (DCU), два акумулятори -- А (Accumulator), що використовується як джерело і приймач при обчисленнях і пересиланнях, та В (Multiplication Register), що використовується як акумулятор лише у командах множення та ділення, і як РЗП – у інших випадках.

Рис. 5. Структурна схема і8051, деталізована до регістрів

Програмно-недоступні буферні регістри T1 і T2 призначені для тимчасового збереження операндів та виконують функції розподілу вхідних та вихідних даних АЛП.

Регістр слова стану процесора PSW (Processor State Word) містить біти, що відображають результати виконання операцій та стан процесора (аналогічний за призначенням регістру прапорів процесора I8086 ).

Адреси комірок ПЗП визначаються вмістом лічильника команд PC (Program Counter) або вмістом регістра-покажчика даних DPTR (Data Pointer Register). Регістр DPTR може використовуватися як один 16-розрядний регістр, або як два незалежних 8-розрядних регістри DPL та DPH.

РПД адресується 8-розрядними регістром адреси PA або покажчиком стеку SP (Stack Pointer) . Регістр адреси є програмно-недоступним регістром, у який завантажується адреса комірки ОЗП під час виконання команд. Регістр SP призначений для адресації вершини стеку, який є частиною РПД.

Регістри P0 – P3 – регістри відповідних портів.

Блок керування складається зі схеми керування та синхронізації CU, генератора OSC та 8-розрядного регістра команд IR. Код команди, зчитаної з РПП, запам’ятовується у IR, і надходить на дешифратор команд, який входить до складу CU . Дешифратор команд формує 24-розряднйи код, що надходить на програмовану логічну матрицю, а після цього – на блок логіки керування.

У складі блоку переривань, таймерів та послідовного порту є наступні регістри:

Регістр керування енергоспоживанням PCON (Power Control Register).

Регістри таймерів/лічильників TL0, TL1, TH0, TH1.

Створюють 16-бітні (Low/High) регістри таймерів/лічильників Т/C0 і Т/C1. Звертання до регістрів тільки байтове.

Регістр режиму таймерів/лічильників TMOD (Timer/Counter Mode Control Register).