Учебное пособие: Мікроконтролери RISC архітектури

– Вбудований аналоговий компаратор.

Основні риси архітектури МК AT90S 2313

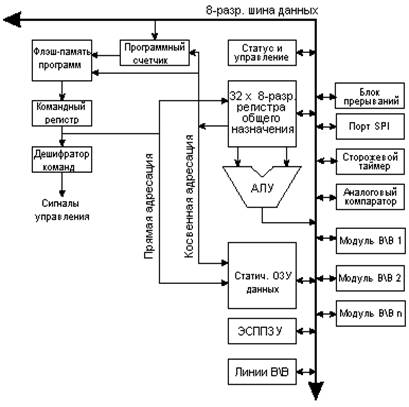

Взаємодія ядра та периферійних пристроїв МК AT90S 2313 зображена на рис. 2. Основна функція ядра ЦП полягає в гарантуванні коректності виконання програми. Крім цього, ЦП повинний мати можливість адресуватися до різних видів пам'яті, виконувати обчислення, керувати периферійними пристроями й обробляти переривання.

Рис. 2. Функціональна схема архітектури AVR.

З метою досягнення максимальної продуктивності і паралельності виконання операцій в AVR -МК використовується Гарвардська архітектура з роздільними пам'яттю і шинами програм і даних. Команди в пам'яті програм виконуються з однорівневою конвеєризацією. У процесі виконання однієї інструкції наступна попередньо зчитується з пам'яті програм. Дана концепція дозволяє виконувати одну інструкцію за один машинний цикл.

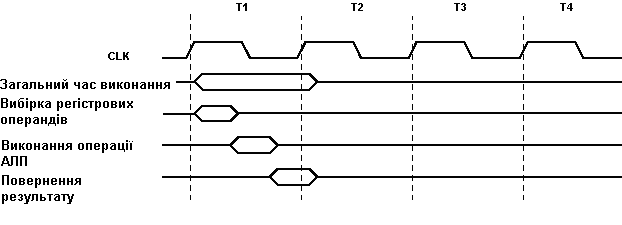

Регістровий файл зі швидким доступом містить 32 x 8-розрядних робочих регістрів загального призначення з однотактовим циклом доступу. Завдяки цьому досягнута однотактність роботи АЛП (див. рис. 3). При звичайній роботі в АЛП спочатку з регістрового файлу завантажується два операнда, потім виконується операція, а після результат відправляється назад у регістровий файл і все це відбувається за один машинний цикл. Шість регістрів з 32 можуть використовуватися як три 16-розрядних регістра непрямої адреси для ефективної адресації в межах пам'яті даних. Один з цих покажчиків адреси може також використовуватися як покажчик адреси для доступу до таблиці перетворення у флеш-пам’яті програм. Дані 16-разр. регістри називаються X -регістр, Y -регістр і Z -регістр.

Рис. 3. Однотактність роботи АЛП.

АЛП підтримує арифметичні і логічні операції між регістрами, а також між константою і регістром. Крім того, АЛП підтримує дії з одним регістром. Після виконання арифметичної операції регістр статусу (прапорів) обновлюється для відображення результату виконання операції. Прапори цього регістра в більшості випадків дозволяють відмовитися від використання інструкцій порівняння, роблячи код програми більш компактним і швидким. Крім того, архітектурою МК підтримуються операції множення зі знаком і без знака і дробовим форматом.

Для розгалуження програми підтримуються інструкції умовних і безумовних переходів і викликів процедур, що дозволяють безпосередньо адресуватися в межах адресного простору. Більшість інструкцій являють собою одне 16-розрядне слово. Кожна адреса пам'яті програм містить 16- або 32-розрядну інструкцію. Пам’ять програм розділена на два сектори: сектор програми початкового завантаження і сектор прикладної програми. Обидва сектори мають роздільні біти захисту від запису і читання/запису. Оскільки всі AVR-інструкції є 16 або 32-розрядними, флеш-пам’ять організована як 1 кбайт х 16. Програмний лічильник РС у МК є 16-розрядним, тому дозволяє адресувати до 64 кбайт пам'яті програм.

При генерації переривання і виклику підпрограм адреса повернення з програмного лічильника записується в стек. Стек ефективно розподілений у статичному ОЗП пам'яті даних і, отже, розмір стека обмежений загальним розміром статичного ОЗП і використовуваним його обсягом. У будь-якій програмі відразу після скидання повинна бути виконана ініціалізація покажчика стека (SP ) (тобто перед виконанням процедур обробки переривань або викликом підпрограм). Покажчик стека – SP – доступний для читання і запису у просторі введення-виведення.

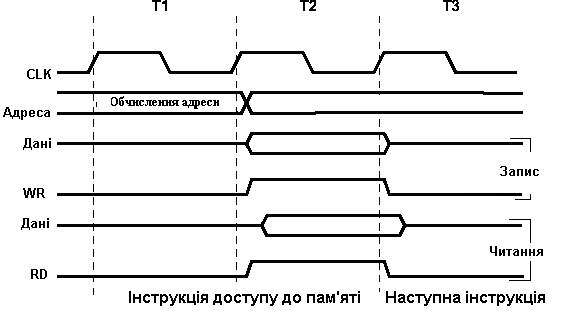

Доступ до статичного ОЗП даних може бути легко здійснений через 5 різних режимів адресації архітектури AVR і виконується за два машинних цикли відповідно до рис. 4.

МК містить 128 байт пам'яті даних типу EEPROM .

Гнучкий модуль переривань містить свої керуючі регістри в просторі введення - виведення і має додатковий біт загального дозволу роботи системи переривань у регістрі статусу. У всіх переривань мається свій вектор переривання відповідно до таблиці векторів переривань. Переривання мають пріоритет відповідно до позиції їхнього вектора. Переривання з меншою адресою переривання мають більш високий пріоритет.

Простір пам'яті введення - виведення містить 32 адреси з безпосередньою адресацією або може адресуватися як пам'ять даних.

Таймери-лічильники МК призначені для точного завдання часових інтервалів, генерації прямокутних імпульсів і виміру часових характеристик імпульсних сигналів.

Рис. 4. Часова діаграма доступу до вбудованого статичного ОЗП даних.

Спеціальні можливості МК

– Скидання при подачі живлення і програмована схема скидання при зниженні напруги живлення.

– Вбудований калібрований RC-генератор.

– Десять зовнішніх і внутрішніх джерел переривань.

- Програмний вибір тактової частоти.

- Шість режимів зниження енергоспоживання:

1.Режим холостого ходу (Idle).

Зупиняє ЦП, але при цьому підтримує роботу статичного ОЗП, таймерів-лічильників, SPI- порту і системи переривань У режимі холостого ходу допускається пробудження від будь-якого зовнішнього або внутрішнього переривання, наприклад, при переповненні таймера.

2. Режим зменшення шумів АЦП (ADC Noise Reduction).

Зупиняє ЦП і всі модулі введення-виведення, крім асинхронного таймера й АЦП для мінімізації імпульсних шумів у процесі перетворення АЦП. Вихід з даного режиму допускається не тільки при генерації запиту на переривання по завершенню перетворення АЦП, але і при зовнішнім скиданні, скиданні по сторожовому таймері, скиданні при неприпустимому зниженні живлення, перериванні при виявленні встановленої адреси на послідовній шині, перериванні по таймеру-лічильнику 0, перериванні по входах INT0, 1.

3. Режим вимикання (Power-down).

У даному режимі припиняє роботу зовнішній генератор, але в дії залишаються зовнішні переривання, спостереження за адресою на послідовній шині і сторожовий таймер (за умови, що вони активізовані). Вихід з даного режиму можливий тільки по зовнішньому скиданню, скиданню сторожовим таймером, скиданню супервізором живлення, перериванні по виявленні встановленої адреси на послідовній шині, перериванні по входах INT0, 1 . У даному режимі фактично відключена генерація всіх тактових частот, тому подальша робота модулів продовжується тільки в асинхронному режимі.

4. Економічний режим (Power-save).

Даний режим ідентичний режимові вимикання за деякими виключеннями:

Якщо Т/С 0 тактується асинхронно, то він у режимі сну продовжить роботу. Вихід з режиму сну можливий по переповненню таймера. У даному режимі зупиняються всі тактові джерела за винятком асинхронних (clkASY), що працюють тільки разом з асинхронними модулями, у т.ч. Т/С 0 з дозволеною опцією асинхронного тактуваня.

5. Режим чергування (Standby).

Кварцовий генератор продовжує роботу, а інша частина МК знаходиться в режимі сну. Даний режим характеризується малою споживаною потужністю, але при цьому дозволяє досягти самого швидкого повернення в робочий режим (за 6 машинних циклів).

6. Розширений режим чергування (Extended Standby).

В даному режимі основний генератор і асинхронний таймер продовжують працювати. Вихід з розширеного чергового режиму відбувається за шість машинних циклів.

Описані вище модулі складають так називаний базовий комплект МК і входять до складу будь-якого сучасного контролера. Очевидна необхідність включення до складу МК додаткових модулів, склад і можливості яких визначаються конкретною розв'язуваною задачею. Серед таких додаткових модулів випливає, насамперед, відзначити:

· модулі послідовного введення/виведення даних;