Учебное пособие: Мікроконтролери RISC архітектури

Полтавський Військовий Інститут Зв’язку

Кафедра схемотехніки радіоелектронних систем

ЛЕКЦІЯ

ОБЧИСЛЮВАЛЬНА ТЕХНІКА ТА МІКРОПРОЦЕСОРИ

Мікропроцесорні системи.

Контролери в телекомунікаціях.

Мікроконтролери RISC архітектури.

Полтава – 2006

Навчальна література:

1. Мікропроцесорна техніка: Підручник/ Ю.І. Якименко та інш. – К.: ІВЦ Політехніка; Кондор, 2004. с. 379-395.

2. Схемотехніка електронних систем: У з кн. Кн. 3. Мікропроцесори та мікро контролери: Підручник/ В.І. Бойко, А.М. Гуржій, В.Я. Жуйков та ін. – 2-е вид. – К: Вища шк., 2004. с. 338 – 356 с.

ВСТУП

CISC МК характеризуються досить розвиненою системою команд, наприклад, МК серії і80х51 мають 111 команд. Однак аналіз програм показав, що 20% з них використовується в 80% випадків, а дешифратор команд займає більше 70% площі кристалу. Команди достатньо складні і виконуються за різний час. Тому у розробників виникла ідея скоротити кількість команд, надати їм єдиний формат і зменшити площу кристала, тобто використати RISC (Reduced Instruction Set Computer) архітектуру.

Особливістю МК, виконаних за RISC архітектурою, є те, що всі команди виконуються за один-три такти, тоді як у CISC контролерах – за один-три машинних цикли, кожний з яких складається з кількох тактів, наприклад для і80х51 – з 12 тактів. Тому RISC контролері мають значно більшу швидкодію. Однак повніша система команд CISC контролерів у деяких випадках сприяє економії часу виконання певних фрагментів програми та економії пам’яті програм.

1. Особливості МК RISC архітектури

У процесорах з RISC-архітектурою набір команд, що виконуються, скорочений до мінімуму. До МК із RISC -процесором відносяться МК AVR фірми Atmel, МК PIC16 і PIC17 (Peripheral Interface Controller) фірми Microchip і інші.

RISC МК мають наступні характерні риси.

1. Всі команди мають формат фіксованої довжини (наприклад, 12, 14 або 16 біт).

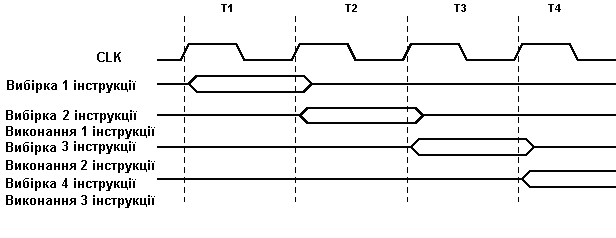

2. Вибірка команди з пам'яті і її виконання здійснюється за один цикл (такт) синхронізації, що ілюструється рис. 1.

Рис. 1. Паралельні вибірки і виконання інструкцій.

3.Система команд процесора припускає можливість рівноправного використання всіх регістрів процесора. У МК із RISC -процесором усі регістри (часто й акумулятор) розташовуються по адресах, що явно задаються. Це забезпечує додаткову гнучкість при виконанні ряду операцій.

На перший погляд, МК із RISC -процесором повинні мати більш високу продуктивність у порівнянні з CISC МК при одній і тій же тактовій частоті внутрішньої магістралі ВКМ. Однак на практиці питання про продуктивність більш складне і неоднозначне.

По-перше, оцінка продуктивності МК за часом виконання команд різних систем (RISC і CISC ) не зовсім коректна. Звичайно продуктивність МП і МК прийнято оцінювати числом операцій пересилання «регістр-регістр», що можуть бути виконані протягом однієї секунди. У МК із CISC- процесором час виконання операції «регістр-регістр» складає від 1 до 3 циклів, що, здавалося б, уступає продуктивності МК із RISC -процесором. Однак прагнення до скорочення формату командRISC- процесора приводить до змушеного обмеження числа доступних в одній команді регістрів. Так, наприклад, системою командМКPIC16 передбачена можливість пересилання результату операції тільки в один із двох регістрів — регістр-джерело операнда або робочий регістр. Таким чином, операція пересилання вмісту одного з доступних регістрів в іншій (не джерело операнда і не робочий) потребує використання двох команд. Така необхідність часто виникає при пересиланні вмісту одного з регістрів загального призначення (РЗП) в один з портів МК. У той же час, у системі команд більшості CISC -процесорів присутні команди пересилання вмісту РЗП в один з портів введення-виведення. Тобто більш складна система команд іноді дозволяє реалізувати більш ефективний спосіб виконання операції.

По-друге, оцінка продуктивності МК по швидкості пересилання «регістр-регістр» не враховує особливостей конкретного реалізованого алгоритму керування. Так, при розробці швидкодіючих пристроїв автоматизованого керування основну увагу варто приділяти часу виконання операцій множення і розподілу при реалізації рівнянь різних передаточних функцій. А при реалізації пульта дистанційного керування побутовою технікою варто оцінювати час виконання логічних функцій , що використовуються при опитуванні клавіатури і генерації послідовної кодової посилки керування. Тому в критичних ситуаціях, що вимагають високої швидкодії, варто оцінювати продуктивність на множині тих операцій, що переважно використовуються в алгоритмі керування і мають обмеження за часом виконання.

По-третє, необхідно ще враховувати, що зазначені в довідкових даних на МК частоти синхронізації звичайно відповідають частоті кварцового резонатора, що підключається, у той час як тривалість циклу центрального процесора визначається частотою обміну по ВКМ. Співвідношення цих частот індивідуально для кожного МК і повинно бути прийняте в розрахунок при порівнянні продуктивності різних моделей контролерів.

2. Однокристальні AVR-мікроконтролери

АрхітектуруRISC МК розглянемо на прикладі AT90S 2313 . Це малопотужний восьмирозрядний КМОП МК, заснований на розширеній AVR RISC -архітектурі. Він належить до сім’ї AVR -МК загального призначення і створений дослідницьким центром фірми Atmel Corp. (Норвегія). Взагалі у номенклатуру групи AT90S входять пристрої з ПЗП від 1 до 8 Кбайт, з різною перефірією, кількість виводів від 8 до 48. Всього випускається три сім’ї AVR -МК – Tiny, Classic, Mega. МК Tiny – найдешевші і мають найпростішу структуру, Mega – найпотужніші, а Classic – займають проміжне положення між ними.

Цей МК сімейства Classic виробляється за технологією високощільної енергонезалежної пам'яті компанії Atmel. Вбудована внутрішньосистемноперепрограмована флеш-пам’ять дозволяє перепрограмувати пам'ять програм безпосередньо усередині системи через послідовний інтерфейс SPI за допомогою простого програматора або за допомогою автономної програми в завантажувальному секторі. Завантажувальна програма може використовувати будь-який інтерфейс для завантаження прикладної програми у флеш-пам’ять. Програма в завантажувальному секторі продовжує роботу в процесі відновлення прикладної секції флэш-памяти, тим самим підтримуючи двохопераційність: читання під час запису. За рахунок об’єднання восьмирозрядного. RISC ЦП з внутрішньосистемносамопрограмованою флеш-пам’яттю в одній мікросхемі, МК дозволяє досягти високого ступеня гнучкості й ефективної вартості при проектуванні більшості додатків вбудованого керування.

Основні характеристики МК AT90S 2313

– 133 інструкцій, більшість з яких виконуються за один машинний цикл;

- Продуктивність: 1 млн. операцій у секунду/Мгц, що дозволяє проектувальникам систем оптимізувати співвідношення енергоспоживання і швидкодії.

– Вбудований пристрій множення виконує множення за 2 машинних цикли.

- Енергонезалежна пам'ять програм 1Кбайт х 16.

– Зносостійкість перепрограмованої флеш-пам’яті: 1000 циклів запис/стирання.

– Зносостійкість EEPROM (128 байт): 100000 циклів запис/стирання.

– Вбудований статичний ОЗП ємністю 128 байт.

–Можливість адресації зовнішньої пам'яті розміром до 64 кбайт.

– Програмований захист коду програми.

– Інтерфейс SPI для внутрішньо системного програмування

- Два 16-розрядних таймера-лічильника.

– 8 каналів 8-розрядного аналогово-цифрового перетворення.

– Послідовний інтерфейс, орієнтований на передачу даних у байтному форматі.

--> ЧИТАТЬ ПОЛНОСТЬЮ <--