Учебное пособие: Мікроконтролери RISC архітектури

· зв'язок вбудованої мікроконтролерної системи із системою керування верхнього рівня, наприклад, з персональним комп'ютером. Найчастіше для цієї мети використовуються інтерфейс RS-232C ;

· зв'язок із зовнішніми стосовно МК периферійними інтегральними схемами, а також з датчиками фізичних величин з послідовним виходом. Для цих цілей використовуються інтерфейси I2 C, SPI , а також нестандартні протоколи обміну;

· інтерфейс зв'язку з локальною мережею в мультимікроконтролерних системах. У системах з числом МК до п'яти звичайно використовуються мережі на основі інтерфейсів I2 C, RS-232C і RS-485 із власними мережними протоколами високого рівня. У більш складних системах усе більш популярним стає протокол CAN .

З погляду організації обміну інформацією згадані типи інтерфейсів послідовного зв'язку відрізняються режимом передачі даних (синхронним або асинхронним), форматом кадру (число біт у посилці при передачі байта корисної інформації) і часовими діаграмами сигналів на лініях (рівні сигналів і положення фронтів при переключеннях).

Число ліній, по яких відбувається передача в послідовному коді, звичайно дорівнює двом (I2 C, RS-232C, RS-485) або трьом (SPI, деякі нестандартні протоколи). Дана обставина дозволяє спроектувати модулі контролерів послідовного обміну таким чином, щоб з їхньою допомогою на апаратному рівні можна було реалізувати кілька типів послідовних інтерфейсів. При цьому режим передачі (синхронний або асинхронний) і формат кадру підтримуються на рівні логічних сигналів, а реальні фізичні рівні сигналів для кожного інтерфейсу одержують за допомогою спеціальних інтегральних схем, що називають прийомопередатчиками, конверторами, трансиверами.

Серед різних типів вбудованих контролерів послідовного обміну, що входять до складу 8-розрядних МК, склався стандарт «де-факто» — модуль UART (Universal Asynchronous Receiver and Transmitter). UART — це універсальний асинхронний приемопередатчик. Однак більшість модулів UART , крім асинхронного режиму обміну, здатні також реалізувати режим синхронної передачі даних.

Модулі аналогового введення/ виведення.

Найпростішим пристроєм аналогового введення в МК є вбудований компаратор напруги . Компаратор порівнює вхідну аналогову напругу з опорним потенціалом VREF і встановлює на виході логічну «1», якщо вхідна напруга більше опорної. Їх зручніше за усе використовувати для контролю визначеного значення вхідної напруги, наприклад, у термостатах. Компаратор дозволяє реалізувати на МК інтегруючий АЦП.

Однак більш широкі можливості для роботи з аналоговими сигналами дає АЦП, вбудований у МК. Найчастіше він реалізується у виді модуля багатоканального АЦП, призначеного для введення в МК аналогових сигналів з датчиків фізичних величин і перетворення цих сигналів у двійковий код.

Власне АЦП виконаний по методу послідовного наближення. Практично у всіх моделях 8-розр. МК розрядність АЦП також складає 8 розрядів. Відповідно, формат представлення результатів виміру АЦП — однобайтовий. Тривалість такту перетворення задає генератор синхронізації: один цикл дорівнює двом періодам частоти генератора tADC . Час перетворення для типових модулів АЦП МК складає від одиниць до десятків мікросекунд.

Момент завершення кожного циклу перетворення відзначається установкою тригера готовності даних. Якщо переривання від модуля АЦП дозволені, то генерується запит на переривання. Як правило, читання регістра результату скидає тригер готовності.

Більшість модулів АЦП мають тільки режим програмного запуску: установка одного з бітів регістра режиму запускає черговий вимір. Найбільш універсальні модулі АЦП мають також режим автоматичного запуску, при якому після завершення одного циклу перетворення негайно починається наступний. Однак дані виміри кожного циклу повинні бути лічені програмним способом.

Цифро-аналогові перетворювачі в складі МК є великою рідкістю. Функція ЦАП реалізується засобами модуля програмованого таймера в режимі ШІМ. На одному з виводів МК формується високочастотна імпульсна послідовність з регульованою тривалістю імпульсу. Отриманий сигнал згладжується фільтром нижніх частот на операційному підсилювачі.

Розширення адресованої пам’яті МК.

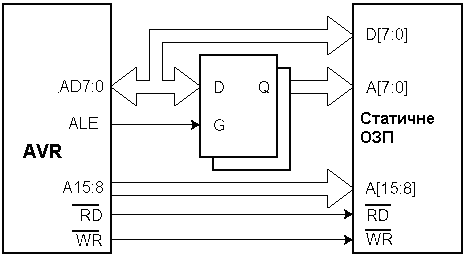

Характеристики інтерфейсу зовнішньої пам’яті дозволяє використовувати його не тільки для підключення до зовнішнього статичного ОЗП або флеш-пам’яті, але і в якості інтерфейсу з зовнішніми периферійними пристроями, наприклад, ЖК- дисплеї, АЦП і ЦАП. Після дозволу зовнішньої пам’яті (XMEM ) стає доступним адресний простір за межами внутрішнього статичного ОЗП через визначені для цієї функції виводи. Інтерфейс складається з:

![]() AD7:0: Мультиплексована молодша шина адреси/шина даних.

AD7:0: Мультиплексована молодша шина адреси/шина даних.

![]() A15:8 : Старша шина адреси.

A15:8 : Старша шина адреси.

![]() ALE : Строб адреси зовнішньої пам’яті.

ALE : Строб адреси зовнішньої пам’яті.

![]() RD: Строб читання із зовнішньої пам’яті.

RD: Строб читання із зовнішньої пам’яті.

WR : Строб запису у зовнішню пам’ять.

Інтерфейс XMEM автоматично визначає до якої пам’яті зовнішньої або внутрішньої здійснюється доступ. Під час доступу до зовнішньої пам’яті інтерфейс XMEM буде формувати сигнали шин адреси, даних і керування на лініях порта у відповідності з рис. 5. При переході ALE з 1 в 0 на лініях AD7:0 будуть присутні дійсні адресні сигнали. ALE знаходиться на низькому рівні під час передавання даних. Після дозволу роботи інтерфейсу доступ до внутрішньої пам’яті буде ініціювати зміни на шинах даних і адреси, а також строба ALE, при цьому, строби RD и WR залишаться незмінними. Рис. 5 ілюструє як підключити зовнішнє статичне ОЗП до AVR - мікроконтролеру за допомогою 8-розр. регістра, який передає дані напряму при високому рівні на вході G .

Рис. 5. Підключення зовнішнього статичного ОЗП до AVR-МК.

Поряд зі створенням складних і високоінтегрованих схем, також удосконалюються мікросхеми, випуск яких був освоєний давно, наприклад, однокристальні ЕОМ сімейства MCS-51. Ці мікросхеми добре зарекомендували себе в недорогих і порівняно нескладних пристроях. Основними напрямками модернізації даних МК є:

· збільшення внутрішньої пам'яті програм до 32 Кбайт, причому вона може бути масочною, одноразово програмованою або з ультрафіолетовим стиранням;

· зниження споживаної потужності шляхом застосування КМОП-технології і спеціальних режимів зниженого енергоспоживання;

· збільшення тактової частоти до 20 Мгц;

· модифікація режимів роботи лічильників-таймерів і послідовного порту;

· розміщення на кристалі додаткового устаткування.

ВИСНОВОК

У процесорах з RISC -архітектурою набір команд, що виконуються, скорочений до мінімуму. Для реалізації більш складних операцій приходиться комбінувати команди.

RISC МК мають наступні характерні риси:

1. Всі команди мають формат фіксованої довжини.

2. Вибірка команди з пам'яті і її виконання здійснюється за один цикл синхронізації.

3. Система команд дає можливість рівноправного використання всіх регістрів ЦП.

МК AT90S 2313 – малопотужний 8-розрядний КМОП МК, заснований на розширеній AVR RISC-архітектурі.З метою досягнення максимальної продуктивності і паралельності виконання операцій в AVR-МК використовується Гарвардська архітектура з роздільними пам'яттю і шинами програм і даних. Команди в пам'яті програм виконуються з однорівневою конвеєризацією. У процесі виконання однієї інструкції наступна попередньо зчитується з пам'яті програм. Дана концепція дозволяє виконувати одну інструкцію за один машинний цикл.