Дипломная работа: Методика расчета и оптимизации ячеек памяти низковольтовых последовательных ЭСППЗУ

Рисунок 7

3.1.3 Зависимость порогов во время записи/стирания

Аналитическое выражение зависимости пороговых напряжений ячейки от времени программирования получается при решении следующего дифференциального уравнения:

DQfg /dt = Atun * Jtun ; (10)

Подставляя это уравнение в (1),(2),(3’),(5’) и (7) получим:

Vtw (t) = Vti + Vg – (1/Kw ) * (B/ln(A * B * t + E1 ); (11)

Vte (t) = Vti – (Vd * Ke )/Kw + 1/Kw * [ B /(ln (A * B * t + E2 )) ]; (12)

Где A = (Atun * a)/(Xtun * (Cpp + Cgox + Ctun )); (13)

B = b * Xtun ; (14)

E1 = exp[ B/(Kw * (Vg + Vti - Vt (0))) ]; (15)

E2 = exp[ B/(Vd * Ke + Kw * Vt (0) + Kw * Vti ) ]; (16)

Vt (0) это пороговое напряжение ячейки при t = 0, которое не может быть спутано с Vti – пороговое напряжение нейтральной ячейки. Atun это область тонкого окисла. Надо отметить, что в уравнении (11) пороговое напряжение остается практически неизменным при t = 0, если Vg прикладывается на время меньшее, чем “характеристическая временная константа” t, которая определяется следующим выражением:

t = (1/AB) * exp[ B/(Kw * (Vg + Vti – Vt (0)) ]; (17)

При больших значениях времени t пороговое напряжение асимптотически приближается к кривой описанной следующим уравнением:

Vtw (t) = Vti + Vg – [ B/(Kw * ln(A * B * t)) ]; (18)

Аналогичное выражение для операции стирания выводится из уравнения (12). Это приближение полезно использовать при проектировании ячеек памяти, а также оно может быть применено для оценки времени программирования, порога окна, операционного времени для любого набора параметров ячейки(A, B, Vti , Kw , Ke ).

3.2 Полная модель ячейки

3.2.1 Расчет плавающего затвора и потенциалов канала

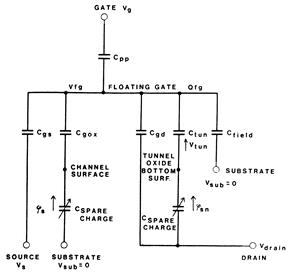

Эквивалентная схема ячейки памяти ЭСППЗУ с учетом паразитных емкостей и емкостей обедненного слоя представлена на рис.8. Эффект утечки дырок в подложку исключен и предположим, что ячейка у нас спроектирована. Cgs и Cgd это емкости перекрытия подзатворного диэлектрика, Cfld это емкость области окисла между плавающим затвором и подложкой. Падение напряжения на емкости обедненного слоя равно fs и fsn для канала и n+ области соответственно. Накопившийся на плавающем затворе заряд Qfg это сумма зарядов всех емкостей:

Qfg = Cpp (Vfg – Vg ) + Cgd (Vfg – Vd ) + Cfld (Vfg – Vsub )

+ Ctun (Vfg – (VD - ½fsn ½))+ Cgs (Vfg -Vs )

+ Cgox (Vsub +½fs ½)); (19)

Во время записи в области n+ накапливается заряд и fsn принимается равным нулю. Канал формируется так, что поверхность канала и свободный исток составляют напряжение на стоке Vd = 0. Таким образом, Vfg может быть вычислено из соотношения (19).

Во время стирания fsn принимается постоянной. Состояние поверхности канала определяет следующий способ нахождения Qfg : во-первых, истощение принято и последний часть в уравнении (17) может быть заменена следующим выражением:

Qdep = Ach * (2q * esi * e0 * Nb * fs )-2 (20)

Для предполагаемого условия Vfg связано с fs следующим соотношением:

Vfg = Vfb + fs + Ach /Cgox * (2q * esi * e0 * fs )-2 (21)

Это выражение включенное в выражение (17) и равнодействующее квадратичное уравнение решено для (fs )-2 . Если уравнение не имеет положительных решений, то поверхность канала накоплена и fs берется равным 0. Напряжение на истоке эквивалентно fs . Уравнение (17) решено для Vfg с учетом fs .

Рисунок 8

4. ЭКСПЕРИМЕНТАЛЬНАЯ ЧАСТЬ

4.1 З апоминающая ячейка

В настоящее время на НПО “Интеграл” используются две разновидности конструкции запоминающей ячейки для ЭСППЗУ: обычная и её масштабированная (уменьшенная) топологическая модификация. Конструктивно ячейки состоят из адресного транзистора (транзистора выборки) и транзистора с «плавающим» затвором, на котором хранится информация.

Для сравнения нами был проведен анализ аналогов ЭСППЗУ, производимых некоторыми зарубежными фирмами: Siemens и Philips.