Контрольная работа: Особенности арифметико-логических устройств (АЛУ) с двоично-десятичными кодами (ДДК) при вычислении операций умножения и деления и поиск путей их ускорения

Умножение ДДК. Анализируется значение очередной тетрады, начиная с младшей и к сумме частичных произведений добавляется множимиое столько раз, какому значению равно число в тетраде. Значение суммы частичных произведений сдвигается вправо на тетраду, чтобы уменьшить количество сложений. Отдельно формируется 8, 4 и 2 кратное множимое (8х, 4х, 2х, 1х). Данная процедура повторяется, пока все тетрады множителя не будут проанализированы.

Деление ДДК. Производится путем многократного вычитания делителя из текущего значения частичных разностей, которые первоначально равны значению делимого, последовательным сдвигом частичных разностей влево по разрядной сетке. Многократное вычитание выполняет до получения отрицательного результата. Количество вычитаний до получения отрицательного результата соответствует очередной цифре частного. В целом, опция похожа на традиционное деление «уголком».

Методы ускорения операции умножения. Аппаратурные методы ускорения требуют дополнительных затрат , пропорциональных количеству обратных разрядов . Как пример к аппартным методам операции (*) – включение дополнительных цепей сдвига возможно за 1 такт алгоритма синхронизировать выполнение сдвига на нескольких разрядах .Другим методом является работы сумматоров , а также совмещение во времени сдвиговых операций и операций суммирования

Логические методы ускорения операции умножения требуют изменения центрального управления . Основным источником повышения эффективности является уменьшение кол-ва сложений выполняемых в процессе получения ![]() S частных произведений . К логическим так же можно отнести методы позволяющие анализировать несколько разрядов множителей одновременно и выполнить соответствующие изменения суммы частных произведений.

S частных произведений . К логическим так же можно отнести методы позволяющие анализировать несколько разрядов множителей одновременно и выполнить соответствующие изменения суммы частных произведений.

Пример лог. метода

![]()

0151413121100=26 –21 ;

k+1 k k-1 0

| | | |

0 1 1 1 0 1 1 1 …….

Вместо 2-Х вычитаний выполняется одно .Если … 0 1к 0 в (к) выполняется только одно сложение

Формализация этого подхода может быть сделана так :

di=(bi + bi-1)*di-1

Si = di *bi+1

bi –логическая переменная определяющая необходимость выполнения арифметической операции для i-того разряда множителя

Si –определяет знак выполнимой операции . Если Si =0 ,то выполняется сложение текущей суммы частного произведения и множимого . Если Si =1 то выполняется “-“ вычитание множимого из суммы частн. Произведений

Данное правило – правило Лемана. Оно при самых неблагоприятных комбинациях разрядов множителей вдвое сокращает кол-во операций суммирования . Среднее значение ускорения *3.

На практике получили применение другие способы операции умножения с анализом нескольких разрядов множителя .

При анализе 2-х разрядов множителя можно предложить след последовательность действий :

Если два разряда 00 . то выполняется только сдвиг S частного произведения (далее S ч.п.)вправо на 2 разряда

Если 01 то к S ч.п. добавляется множимое , а далее выполняется сдвиг на два разряда

Если 10 то к S ч.п добовляется удвоеное множимое и S ч.п сдвигается вправо на два разряда, если 11 то вычитаем множимое и на специальном триггере запоминается ситуация о необходимости коррекции при анализ след 2-х разрядов. Далее S ч.п сдвигается вправо на два разряда , след пара разряда множителя уже рассматривается как увел на 1.

| Значение разрядов | Операция при знаке предыдущего разрядов <1000 | Операция при знаке предыдущего разрядов >=1000 |

| 0000 | П(4)z | П(4)(z+x) |

| 0001 | П(4)(z+x) | П(4)(z+2x) |

| 0010 | П(4)(z+2x) | П(4)(z+3x) |

| 0011 | П(4)(z+3x) | П(4)(z+2x+2x) |

| 0100 | П(4)(z+2x+2x) | П(4)(z+2x+3x) |

| 0101 | П(4)(z+2x+3x) | П(4)(z+6x) |

| 0110 | П(4)(z+6x) | П(4)(z+x+6x) |

| 0111 | П(4)(z+x+6x) | П(4)(z+2x+6x) |

| 1000 | П(4)(z+2x+6x) | П(4)(z-x-6x) |

| 1001 | П(4)(z-x-6x) | П(4)(z-6x) |

| 1010 | П(4)(z-6x) | П(4)(z-2x-3x) |

| 1011 | П(4)(z-2x-3x) | П(4)(z-2x-2x) |

| 1100 | П(4)(z-2x-2x) | П(4)(z-x-2x) |

| 1101 | П(4)(z-x-2x) | П(4)(z-2x) |

| 1110 | П(4)(z-2x) | П(4)(z-x) |

| 1111 | П(4)(z-x) | П(4)z |

Указанные значения соответствуют кратным множимого, которые создаются и хранятся отдельно. Очевидно, можно получить похожую схему при анализе большего количества разрядов. На практике используются также табличное умножение, которое с помощью соответствующих элементов памяти позволяет для определённых комбинаций двоичных разрядов сразу получить соответствующее значение, которое прибавляют к текущему значению суммы частичных произведений перед сдвигом её вправо на требуемое значение разрядов.

Табличное умножение значительно ускоряют операцию, используемую во всех моделях процессора Pentium. Целочисленное умножение является составной частью умножения чисел с плавающей точкой, поэтому эффективность данной операции существенно влияет на эффективность операции с плавающей точкой. Дополнительно для ускорения выполнения операции умножения используется конвейерная форма организации, при которой сочетаются во времени различные фазы или элементы операции, выполняемые над разными последовательностями операндов. Именно наличие последовательностей позволяет поднять общую производительность операции.

АЛУ для реализации операции деления. Операция / является обратной по отн к операции *, поэтому общая структура операции заключается в последовательности вычитания значения делителя из делимого и сдвигах.

Результат в виде текущего значения частичных разностей. Цифры частного определяются как при положительном значении частичных разностей и как нуль в противном случае.

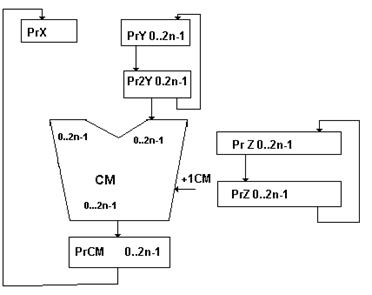

Рассм. осн. требования: Частное Z как рез-т деления делимого X на делитель Y, Z=X/Y. Х представляется в формате двойного слова, т.е. занимает (2n-1) разрядов, Z и Y представлены в формате одинарного слова, т.е. занимают (n-1)разрядов. Поэтому |Z|<2n-1. Для того, чтобы частное размещалось в формате двойного слова необходимо |X’|-|Y|<0, где |X’|=|X|-2-(n+1). В противном случае частное не может быть размещено в формате одного слова. Поэтому операция деления невыполнима. Для поверки этого условия выполним пробное вычитание. Для этого выравнивают делимое и делитель так, чтобы младший разряд делителя был под (n-1)-м разрядом делимого.если вычитание даст отрицательный результат, то операция продолжается. По сути дела мы реализовали традиционное деление «в столбик».Т.о. для выполнения операции деления необходимо либо сдвигать вправо делитель по разрядной сетке, начиная со старших разрядов в процессе получения частичных разностей. При этом делимое остается неподвижным. Либо можно сдвигать влево значение делимого при неподвижном делителе. В процессе получения частичных разностей очередная цифра частного определяется знаком текущего значения частичных разностей. Исходя из этого может быть построено 2 варианта АЛУ.(СХЕМА)

Данная схема предполагает использование двойной разрядности всех элементов. При этом делимое и послед. значение частичных разностей неподвижны, а сдвигаются вправо компоненты делителя. Начальное положение делителя старшие разряды регистра РгУ, а затем делитель - из результате каждой итерации. Частичные разности получаются с помощью сумматора, на один вход которого подается делимое, а на другой-обратный код делителя. Доп. код получается подсуммированием 1 к младшему разряду сумматора. Цифры частного формируют по знаку полученных частичных разностей, т.е. по нулевому разряду сумматора. Цифры заносятся в младший разряд регистра РгZ, которые передаются со сдвигом влево в регистр Z’, а далее прямо в регистр Z. Основным недостатком этой схемы является использование двойной разрядности всех компонентов. На практике получила распространение схема с неподвижным делителем и сдвигаемым влево значением частичных разностей.(СХЕМА).