Контрольная работа: Розробка структурної схеми процесорного елемента та мікропрограми керування для реалізації команди

4. Система команд AVR-контроллеров — http://ntlib.chat.ru/avr/instr.htm

5. Документація на мікроконтроллерифірмиIntel MCS-51/151/251. (каталог pdfфайлів) — http://www.intel.com/design/mcs51/docs_mcs51.htm

ДОДАТКИ

Додаток 1

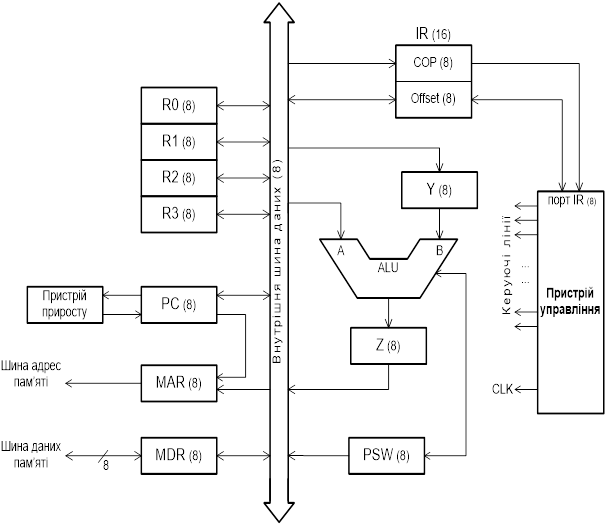

Рис 2.Структурна схема процесорного елемента

Додаток 2

Розшифровка позначень на схемі

Таблиця1

| Символьнепозначення | Опис |

| R0, R1, R2, R3 | Регістри загального призначення, використовуються програмістами для потреб програм. |

| Z | Регістр, призначені для тимчасового збереження результату виконання певної операції арифметико-логічним пристроєм. |

| Y | Регістр для тимчасового збереження операнду, який потрібно обробити в АЛП. |

| IR |

(Instruction register) Регістр, в якому зберігається код машинної команди. |

| ALU |

(Arithmetical-logical unit) Арифметико-логічний пристрій, АЛП |

| PC | (Program counter) Лічильник команд |

| MAR | (Memory address register) Регістр адрес пам’яті |

| MDR | (Memory data register) Регістр даних пам’яті |

| PSW | (Program status word) Регістр стану |

Додаток 3

Лістинг мікропрограми

consts.inc

R0_inEQUp1.0

R0_out EQU p1.1

R1_in EQU p1.2

R1_out EQU p1.3

R2_in EQU p1.4

R2_out EQU p1.5

R3_in EQU p1.6

R3_out EQU p1.7

PC_in EQU p3.0

PC_out EQU p3.1

PC_to_MAR EQU p3.2

MFC EQU p3.3

MAR_in EQU p3.4

MRead EQU p3.5

MDR_in EQU p3.6

MDR_out EQU p3.7

IRcop_in EQU p0.0