Курсовая работа: Компютерна схемотехніка 2

- синхронні

- асинхронні

3. за кількістю сигналів, що використовуються для керування:

- однофазні

- парафазні

4. за основним призначенням:

- регістри пам’яті

- регістри зсуву

Будують регістри на основі періодичних структур, кількість яких визначається розрядністю запам’ятовуючих слів. Структурно вони складаються з елементів пам'яті та комбінаційних схем керування. Останні забезпечують синхронний запис та зчитування інформації, обнулення та ін. В багато контактних схемах застосовуються двоступінчасті тригери, які комутуються з допомогою динамічних сигналів, тобто з допомогою динамічних перепадів логічних "0" та "1".

Паралельні регістри

Паралельні регістри синхронного та асинхронного типу найпростіше синтезувати на основі паралельного ввімкнення RS-тригерів. При цьому сигнал тактового запису та обнулення запаралелюється, а інформаційні входи призначаються для паралельного подання на них потрібних кодових слів.

Запис всіх біт інформації здійснюються за допомогою одного тактового імпульсу. Якщо для обнулення інформації чи запису використати парафазні сигнали, які подаються на кожен біт (тригер) окремо, то кажуть, що така схема працює за парафазною схемою керування. Для одержання нового інформаційного слова в інверсному вигляді можна використовувати інверсні Q виходи тригерів. Аналогічно для реалізації двофазної схеми паралельного регістра можна використати інформаційні D-тригери. В такому регістрі сигнали реалізації теж запаралелені.

В якості елементів пам’яті використовують комірки на основі складних елементів 2, 2І-АБО, а також D-тригери, в яких реалізовано зворотній зв'язок для двох ступенів. Сигнали синхронізації (С) та обнулення (R) запаралелені для всіх комірок і подаються на відповідні входи D-тригерів. Дозвіл запису вхідних інформаційних сигналів D забезпечується керуючими сигналами Е1 , Е2 , ввімкненими за схемою АБО з додатною інверсією входу. Вхідні елементи DD1 та DD2 дозволяють розділити режими запису та зберігання інформації. Сигнали Ez 1 i Ez 2 також ввімкнені за схемою диз’юнкції при інверсії і забезпеченні переведення входів регістру Qi у високоімпедансний стан.

Для запису сигналів з різних джерел можна використовувати комбінаційні схеми 2, 2І-АБО, які забезпечують синхронізацію подачі сигналів S та R на комірки пам’яті. Керування комутацією різних джерел реалізується з допомогою двопозиційного коду С1 С2 .

В залежності від двійкового коду С1 С2 на вхід установки комірки регістру подається вхідний сигнал Х або У. синхронно з ним інверсні сигнали записуються на вхід R. Розрядність нарощування регістрів не обмежується за кількістю інформаційних сигналів, однак в реальних схемах потрібно враховувати допустимі значення коефіцієнтів розгалуження за виходом базових логічних елементів, що застосовуються в комбінаційних схемах керування, щоб не допустити зменшення вихідного рівня сигналу за мінімальне значення логічної одиниці.

Регістри зсуву

В схемах зсуву запис багаторозрядного коду розрядністю n здійснюється за n тактів синхронізації. При цьому найстарший біт постійно перезаписується в усі комірки багаторозрядного регістра. Схему такого регістра можна реалізувати з допомогою базових комірок на основі комбінаційних RS та D-тригерів.

Режим роботи схеми визначається сигналом, що подається на вхід s/p (мікросхема DD2). При нульовому значенні s/p інвертор DD2 подає логічний рівень 1 на DD4, DD6. Це забезпечує інвертування сигналу на входах R, що дозволяє проходження паралельного двійкового коду інформаційних входів D0 , D1 на входи установки RS-тригерів. Запам’ятовування інформації здійснюється за тактовим перепадом імпульсу на входах з високого до низького рівня. Наявність DD4, DD6 забезпечує неоднозначність сигналів на RS-входах. Зміна вхідного s/p сигналу приведе до блокування входів D0 , D1 і запис інформації можливий з інформаційного входу V, з’єднаного з D-входом інформаційного тригера DD7. За такт перепадом синхроімпульсу С інформація з виходу Q DD7 записується на вхід DD8. Таким чином реалізується послідовний зсув інформації за кожним тактовим імпульсом на одну позицію вправо.

Розрізняють одно- та двонаправні регістри зсуву. В перших реалізується на схемотехнічному рівні зсув тільки вліво або тільки вправо. В других схемотехніка дозволяє з допомогою програмованого входу реалізувати зсув чи вліво, чи вправо. В умовних позначеннях це відображається стрілкою.

8. Класифікація, різновидності, функціонування лічильників. Переваги та недоліки послідовних і паралельних схем лічильників. Їх швидкодія і складність. Двійкові та двійково-кодовані лічильники

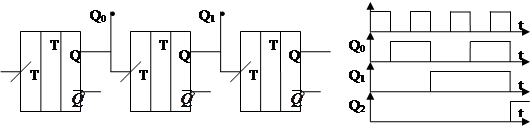

Лічильниками називаються послідовні логічні пристрої, призначені для перерахунку кількості імпульсів, а також для зберігання цієї інформації в двійковому коді. Будують їх на основі динамічних Т-трігерів. В залежності від схеми комутації тригерів та комбінаційної схеми керування лічильники можуть забезпечувати як додавання одиничних імпульсів, тобто виконання функцій інкрименту, так і віднімання – функція декрименту.

До основних параметрів лічильників відносять модуль перерахунку та час встановлення вихідного двійкового коду. За модулем перерахунку їх поділяють на двійкові ( М = 2n ) та двійково-кодовані, наприклад, двійково-десяткові, тобто з нецілочисельним модулем М. За напрямком перерахунку: лічильники з додаванням, відніманням та реверсивні.

За способом організації міжкаскадних зв’язків виділяють лічильники з послідовним, паралельним та комбінованим переносом.

Найпростіше реалізовуються схеми з послідовим переносом на динамічних Т-тригерах. В цьому випадку вихід попереднього каскаду вмикається на вхід наступного.