Курсовая работа: Компютерна схемотехніка 2

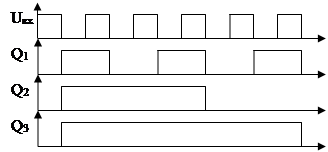

Якщо використати однойменні вхідні-вихідні сигнали, то реалізується функція віднімання, епюри напруг якої зображені на малюнку.

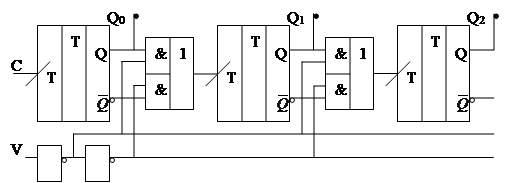

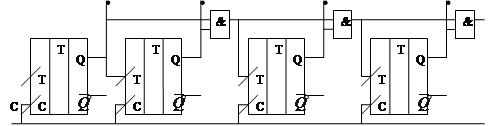

Таким чином, досить просто реалізувати реверсивний лічильник, використовуючи змінну комутацію вихідного сигналу при постійному значенні динамічного входу. Для цього звичайну схему динамічного лічильника доповнюють елементами складної логіки 2,2 І-АБО. Схема керування доповнюється двома інверторами , які забезпечують пере комутацію сигналів з виходів складних елементів.

Сигнал V визначає напрямок перерахунку додавання чи віднімання. Вхідні тактові імпульси подаються на вхід С першого тригера . Якщо V = 1, то на перший елемент І комбінаційного пристрою 2,2 І – АБО подається значення логічного нуля, на другий – значення логічної одиниці, тобто в цьому випадку інформаційним сигналом є сигнал з інверсного виходу ![]() тригера. При прямому динамічному вході реалізується схема додавання.

тригера. При прямому динамічному вході реалізується схема додавання.

Якщо V = 0, активним стає прямий вихід тригера і маємо реалізацію схеми віднімання.

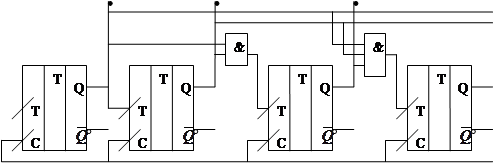

При реалізації схеми віднімання, якщо маємо обтулені значення Q за першим тактовим імпульсом, в тригер записується максимальне значення коду – всі одиниці і з кожним тактовим імпульсом проводиться віднімання по одному двійковому числу. Загальним недоліком є зростання часу комутації результуючого вихідного стану лічильника при зростанні загальної його розрядності. Для усунення цього недоліку використовуються лічильники з паралельним переносом, тоді схеми послідовних лічильників доповнюють комбінаційними елементами, які враховують в кожному наступному розряді стани всіх попередніх розрядів, що реалізуються функцією кон’юнкції.

Обов’язковою умовою схем паралельного переносу є використання синхронізуючого С – входу. Недоліком є зростання числа входів в кон’юнкторах із зростанням розрядності лічильника, оскільки вони повинні забезпечувати реалізацію функції множення за модулем 2.

Для І розряду формуючий сигнал залишається асинхронним, тому його приймають рівним 1. В лічильнику з паралельним переносом напрямок перерахунку не залежить від вибору типу вхідного стану (прямого чи інверсного), він визначається тільки використаними вихідними сигналами Q або ![]()

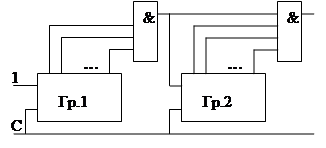

![]() , тому реалізувати реверсивну схему можна аналогічно до схеми послідовного лічильника. Для усунення недоліків паралельних схем і підвищення швидкості перерахунку використовуються комбіновані схеми паралельно-послідовного переносу, при цьому лічильник розрядності n, меншої за загальну розрядність m лічильника, є базовою групою, в якій реалізовано паралельний підрахунок. Передача комутаційних сигналів між групами реалізується послідовно.

, тому реалізувати реверсивну схему можна аналогічно до схеми послідовного лічильника. Для усунення недоліків паралельних схем і підвищення швидкості перерахунку використовуються комбіновані схеми паралельно-послідовного переносу, при цьому лічильник розрядності n, меншої за загальну розрядність m лічильника, є базовою групою, в якій реалізовано паралельний підрахунок. Передача комутаційних сигналів між групами реалізується послідовно.

Максимальне значення часу перемикання визначається часом комутації тригерів у окремій групі. При цьому потрібно враховувати загальний максимальний час, який залежить від кількості груп багаторозрядного лічильника l:

t під. ьакс. = t зр. ( l – 1 ).

В загальному випадку кількість тригерів в кожній групі може бути довільною і навіть рівною 1, тому паралельно-послідовну схему можна реалізувати для окремих розрядів, Така схема називається схемою з наскрізним переносом.

В такій схемі комутація тригерів відбувається практично одночасно, необхідно враховувати тільки час затримки на комутацію одного окремого розряду із врахуванням часу затримки в комбінаційній схемі. Підвищення швидкодії досягається за рахунок того, що час перемикання комбінаційної схеми менший за час комутації тригера.

9. Керуючі автомати АЛП. Синтез керуючих автоматів зі схемною логікою. Структурна схема та алгоритм структурного синтезу автоматів зі схемною логікою

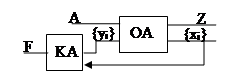

Арифметико – логічним пристроєм називаються функціонально завершені вузли ЕОМ і призначені для використання арифметичних операцій та логічної обробки даних, які представлені у вигляді двійково-кодованих інформаційних сигналів. Такі вузли можна реалізувати за допомогою схемотехнічних пристроїв, функціонування яких визначається на апаратному або програмному рівні, тобто в пристроях з жорсткою або програмованою логікою. В загальному випадку АЛП складаються з операційного та керуючого автоматів.

Операційний автомат призначений для безпосереднього виконання арифметичних операцій, згідно керуючих сигналів {yi }, та даних А, які на нього поступають. Результат виконання операцій індукується на Z-виходах. Сукупність вихідних сигналів {xi } несе інформацію про отримані результати та разом з вхідними керуючими сигналами F формує сигнали мікрокоманд yi .

Синтез керуючих автоматів зі схемною логікою

Основі синтезу структури таких автоматів розроблені академіком Глушковим.

Згідно канонічного методу, структурний синтез описується законами функціонування абстрактного автомату, який реалізується з допомогою комбінаційних схем та наборів тригерів – RS, JK, D, T. Тригери є елементарними автоматами, реалізованими за принципом Мура. Вони характеризуються двома логічними станами, що до?