Курсовая работа: Многопроцессорный вычислительный комплекс

Общее функционирование комплекса ничем не отличается от работы простой ЭВМ общего назначения. Отличие в том, что после формирования сигналов MRDC или MWDC одним процессором, начинает отслеживаться ситуация, когда эти сигналы сформирует другой процессор и перевод этого процессора в состояние ожидания. После завершения работы с памятью первый процессор формирует сигнал, переводящий второй процессор из состояния ожидания в рабочий режим.

3. Выбор и обоснование элементов

Описание микропроцессора 80386:

1. Вывод – ВНЕ – выходной сигнал разрешения передачи старшего байта, активный – низкий.:

2. Выводы S 0, S 1 – выходные сигналы состояния. Вместе с М/-IO,COD/ -INTA определяют текущее состояние микропроцессора.

3. Выводы PEREQ ,– PEACK – входной и выходной сигнал соответственно. Запрос от сопроцессора и подтверждение сопроцессору. Не используется.

4. Выводы А23 – А0 – выходы на шину адреса. Разряды А23 – А16 во время обращения к портам равны нулю.

5. Выводы D 15 – D 0 – двунаправленная шина данных.

6. Вывод CLK – входной сигнал синхронизации микропроцессора, внутри делится на 2.

7. Вывод RESET – входной сигнал сброса микропроцессора. Активный– высокий. Минимальная длительность – 16 тактов системного синхросигнала.

8. Вывод M /- IO – выходной сигнал, позволяет отличить обращение к памяти от обращения к порту.

9. Вывод COD /- INTA – выходной сигнал, позволяет отличить цикл выборки команды от цикла чтения данных и цикл подтверждения прерывания от цикла чтения/записи порта.

10. Вывод – LOCK – выходной сигнал блокировки захвата шины. Активизируется по команде LOCK или в цикле подтверждения прерывания.

11. Вывод – READY – входной сигнал готовности шины. Завершает цикл шины. Активный – низкий. Игнорируется во время активного сигнала HLDA.

12. Выводы HOLD , HLDA – входной и выходной сигналы соответственно. Запрос на захват шины и подтверждение захвата.

13. Вывод INTR – входной сигнал запроса на прерывание.

14. Вывод NMI – входной сигнал немаскируемого запроса на прерывание. Циклы подтверждения прерывания не вырабатываются.

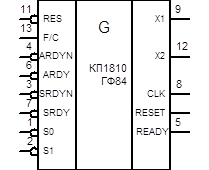

Описание синхрогенератора К1810ГФ84.

Синхрогенератор ( или генератор тактовых импульсов ) К1810ГФ84 служит для синхронизации работы процессора и других периферийных микросхем. Он также синхронизирует сигнал готовности READY при его генерации асинхронными микросхемами или схемами с иной синхронизацией. Также генерирует сигнал RESET сброса процессора при включении питания или при нажатии кнопки RESET (сброс).

|

Конструктивно микросхема выполнена по CMOS–технологии в корпусе с 18 выводами, расположенными в два ряда.

Описание выводов микросхемы: CLK – системная синхронизация, используеncz микропроцессором и другими микросхемами, работа которых должна быть синхронной с ним (частота выхода CLK равна удвоенной внутренней процессорной частоте и определяется частотой используемого кварца, а именно равна 12 МГц); F/C – выбор частоты/кристалла, определяет источник для создания синхронизирующего сигнала CLK(когда F/C=0 для генерации CLK используется внутрисхемный осциллятор, если F/C=1, то используется входной сигнал, подаваемый на вход EFI); EFI – этот вход управляет генерацией сигнала CLK, если F/C=1 (в PC/AT не используется);Х1,Х2 – через эти выводы кварц подсоединяется к внутреннему генератору для создания колебательного контура;

PCLK – это выход синхросигнала с частотой, равной половине частоты CLK (в PC/AT не используется);ARDYEN – это сигнал разрешения асинхронного входа готовности, выделяет сигнал ARDY, используемый для удлинения текущего цикла шины;ARDY – это входной асинхронный сигнал для образования выходного сигнала READY на удлинение цикла шины; SRDYEN – этот входной сигнал аналогичен ARDYEN, но только он синхронный, выбирает SRDY как источник формирования выходного сигнала READY; SRDY– это входной сигнал синхронизированной готовности, должен быть синхронизирован относительно CLK; S0,S1 – эти входы соединены с выводами S0,S1 процессора, давая синхрогенератору информацию о цикле шины;READY – это выходной сигнал готовности, который разрешает завершение текущего цикла шины;RES – это входной сигнал ‘входной сброс’, который разрешает выходной сигнал RESET синхрогенератора; RESET – это выходной сигнал, который появляется при подаче сигнала разрешения на вход RES (используется для перевода всей системы в начальное состояние);

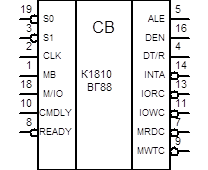

Описание шинного контроллера К1810ВГ88.

|

?????? ?????????? ?1810??88 ???????????? ??? ????????? ????????, ??????????? ?????????? ??????? ????: ??????? ??????? ????? ??????????? ? ????????????? ????????????, ? ????? ??? ????????????? ???? ??????? ? ??????? ?????????? ? ?????? ?????????. ??? ???? ??? ?????????? ???????????????? ???????? PROCCLK ?? ??1810??84.

Конструктивно контроллер выполнен в корпусе с 20 выводами с двухрядным их расположением.

Описание выводов микросхемы: CLK – системная синхронизация, входной сигнал, идущий от синхрогенератора КП1810ГФ84; S0,S1,M/IO – это входные сигналы, с дешифрации которых контроллер начинает свою работу по выполнению совместно с процессором очередного цикла шины ( расшифровка различных комбинаций этих сигналов приведена при описании выводов процессора с теми же названиями);МВ– это входной сигнал выбора режима шины MULTIBUS;READY– сигнал на этом входе, указывает на окончание текущего цикла шины;CMDLY– этот входной сигнал позволяет задержать начало работы контроллера по выполнению очередного цикла шины; CENL– это входной сигнал, называемый разрешением защелкивания команды (в PC/AT на этот вход должна подаваться логическая единица);CEN/AEN– это входной сигнал, называемый ‘разрешение команды/разрешение адреса’;ALE – это выходной сигнал, называемый ‘разрешение защелки адреса’;DEN– это выходной сигнал разрешения передачи данных, определяет передачу данных со входов на выходы в шинных формирователях, подсоединенных к системной шине; DT/R – это выходной сигнал, определяющий направление передачи данных ( микросхема DD14 используется для передачи младшего байта данных, а DD13 – старшего байта данных);MCE – это выходной сигнал разрешения каскадирования (в PC/AT не используется); INTA – это выходной сигнал подтверждения аппаратного прерывания;IORC – это выходной сигнал управления, сообщающий периферийному устройству, что оно должно выставит данные на шину для последующего их чтения процессором;IOWC - это выходной сигнал управления, информирующий о протекании цикла шины записи данных в периферийный порт; MRDC– это выходной сигнал, сообщающий о проведении цикла шины чтения данных из ОП; MWTC– этот выходной сигнал информирует о протекании цикла шины записи данных в ОП.

Описание буферного регистра КП580ИР82.

Используется для организации запоминающих буферов, адресных защелок, портов ввода-вывода и тому подобное. Буферные регистры состоят из восьми информационных триггеров с трехстабильными выходами, общими сигналами записи информации и управления выходными схемами.

|

Назначение выводов: D7 – D0 – линии входных данных; Q7 – Q0 – линии выходных данных; C- стробирующий сигнал; CS – разрешение выдачи данных. Регистр принимает и отображает информацию синхронно с положительным перепадом тактового импульса, подаваемого на вход С. Состояния регистра приведены в таблице.

| Входы | Выход триггера | Выходы | |||

| CS | С | Dn | Q | Q0..Q7 | |

| 0 | 0 | 0 | 0 | ||

| 0 | 1 | 1 | 1 | ||

| 1 | 0 | 0 | Z | ||

| 1 | 1 | 1 | Z | ||

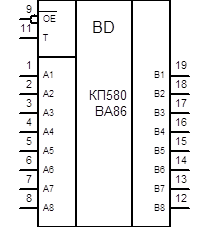

Описание шинного формирователя КП580ВА86.

Применяются как буферные устройства шины данных в микропроцессорных системах. Большая выходная мощность и простота управления позволяет использовать их для построения двунаправленных согласующих буферов межмодульной связи.

|

????????????? ??????? ?? ?????? ?????????? ?????????????? ?????? ? ?????? ????????? ?????????? ? ? ??. ?????????????? ????? ??????? ?? ???? ??????????-?????????????? ? Z-??????????? ?? ???????, ????? ????????? ??????? ???????????? ????????????????? ????????.

Назначение выводов: А7 – А0 – вход-выход линий данных. В зависимости от состояния входа Т они могут быть входными, если Т=1 и выходными, если Т=0; В7 – В0 – вход-выход линий данных. Аналогично А7 – А0.

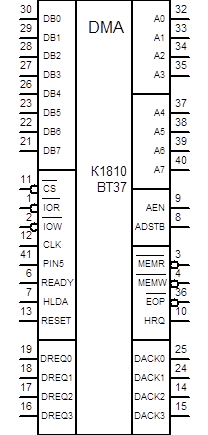

Описание контроллера ПДП К1810ВТ37.

Используется в составе МПВК для реализации прямого доступа к памяти по четырем независимым каналам с положительными или отрицательными приращениями адреса. Каждый канал может выполнять до64К циклов ПДП иимеет возможность автоматической инициализации, то есть повторения циклов ПДП с теми же параметрами.

|