Курсовая работа: Многопроцессорный вычислительный комплекс

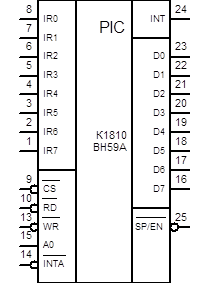

Описание контроллера прерываний К1810ВН59А.

Все запросы на аппаратные прерывания из системной шины направляются через контроллер прерываний К1810ВН59А. Этот контроллер генерирует запросы прерываний на вход INTR микропроцессора. Контроллер может принимать сигналы прерываний от нескольких устройств, назначать им приоритеты и прерывать работу процессора.

|

Описание выводов контроллера: D7 – D0 – двунаправленная шина данных; INTA – вход подтверждения прерывания, разрешающий контроллеру выдать вектор прерывания на шину данных; IRQ7 – IRQ0 – асинхронные входные сигналы запросов прерываний; INTR – выходной сигнал действительного запроса на прерывание для прерывания процессора и организации обработки возникшего прерывания; SP/EN – в PC/AT не используется; CS – вход выбора контроллера, разрешающий связь между процессором и контроллером при активных IOR или IOW; WR – вход запись, разрешающий программирование контроллера; RD – вход чтение, разрешающий считывание некоторых регистров контроллера; A0 – вход адреса, использующийся совместно с CS, WR или RD для записи/считывания внутренних регистров контроллера.

|

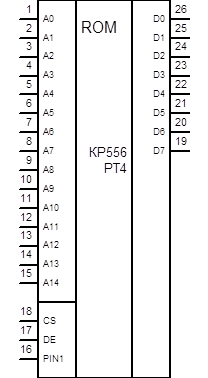

Описание микросхемы ПЗУ КР556РТ4. Микросхема имеет емкость 32 кбайта и представляет собой перегружаемую ПЗУ. Имеет 15 адресных входа и 8 выходов данных. Сигналы CS и DE для выбора данной микросхемы. Выход PIN1 для перепрограммирования не используется.

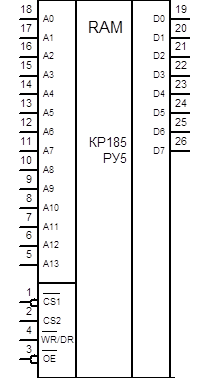

Описание микросхемы ОЗУ КР158РУ5.

Микросхема имеет емкость 256 кбайта и представляет собой оперативное запоминающее устройство. Имеет 14 адресных входа и 8 выходов данных. Сигналы CS1 и CS2 для выбора данной микросхемы. На них подается А15 с системной шины для отличия обращения к ПЗУ от ОЗУ ( для ОЗУ А15=0 ). Выход WR/RD для определения операции чтения или записи. Сигнал ОЕ не используется.

|

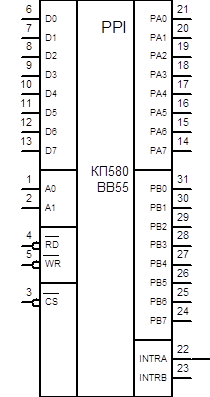

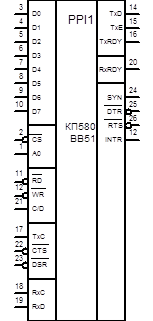

Описание контроллера параллельных ПУ КР580ВВ55.

Используется для организации параллельного обмена данными между процессором и ПУ. Позволяет подключать до 2 устройств.

Назначение выводов: D7 – D0 – двунаправленная шина данных; А0,А1 – адресные входы для выбора требуемого ПУ; RD,WR – выбор операций чтения или записи; CS – выбор данной микросхемы; PA7 – PA0, PB7 - PB0 – шины данных к ПУ; INTA, INTB – выводы запросов на прерывания.

|

Описание контроллера последовательных ПУ КР580ВВ51.

|

???????????? ??? ?????????? ?????????-??????????? ??????-??????? ????? ????????????????? ?? ? ???????????.

4. Разработка принципиальной схемы

Принципиальная схема МПВК приведена в приложении схема 3.

В схеме используется микропроцессор фирмы Intel 80386. Он имеет двадцатичетырехразрядную шину адреса, но так как восемь старших разрядов не используются, то они заведены на землю. В данной реализации мы обходимся шестнадцатью разрядами адреса, так как адресуемая память имеет размер 640 кбайт. Сигналы, необходимые для работы с сопроцессором также не используются.

Для реализации буферного шестнадцатиразрядного регистра используются два восьмиразрядных регистра КП580ИР82.

Для реализации шестнадцатиразрядного шинного формирователя используются два восьмиразрядных формирователя КП580ВА86.

ПЗУ на 256 кбайта собрано на микросхемах КР556РТ4 емкостью 32 кбайта.

ОЗУ на 640 кбайт собрано на микросхемах КР185РУ5 емкостью 256 кбайт.

Заключение

Проблема повышение быстродействия ЭВМ наиболее ощутима в настоящее время, так как повышение быстродействия за щет изобретения новых микросхем или использования новых технологий в настоящее время почти невозможно. Приходится решать эту проблему используя уже существующую базу. Многопроцессорный комплекс является одним из наиболее успешных решений данной проблемы.

В данном курсовом проекте не использовались отдельные каналы ввода-вывода для подсоединения ПУ непосредственно к памяти, а использовалось подключение через системную шину. Это дало бы возможность полностью освободить системную шину и предоставить ее полностью в распоряжение компьютера. Единственный недостаток оставшийся в МПВК после этого – это простои процессоров в случае одновременного обращения к памяти. Эта проблема решается за счет действительно многопортового ОЗУ.

Литература

1. Ларионов А. М. и др. Вычислительные комплексы, системы и сети. - Л. : Энергоатомиздат, 1987.

2. Цифровые интегральные микросхемы: Справ. / Богданович М. И. и др. – Мн. : Беларусь, 1991.

3. Конопелько В. К. , Лосев В. В. надежное хранение информации в полупроводниковых ЗУ. – М. Радио и связь, 1986.

4. Полупроводниковые БИС запоминающих устройств: Справочник / под ред. А. Ю. Горбунова – М. : Радио и связь, 1986.

5. Левкин В.Г.,Левкина А.И. Введение в схемотехнику IBM PC/AT. – Мн. : Беларусь,1982.

6. Руководство по архитектуре IBM PC/AT,/ под ред. М.Л. Мархасина. – Мн. : 1993.

7. Качан М.К. Электронные вычислительные машины и системы. Киев.1985.

8. Русак И.М.,Луговской К.Л. Технические средства ПЭВМ. Справочник. Москва. 1984.

9. Микропроцессорный комплекс К1810: структура, программирование, применение. Справочник. Москва. Высшая школа. 1990.