Курсовая работа: Моделирование работы приемника циклового синхросигнала аппаратуры ЦСП

формирование сигнала установки цифрового оборудования передачи ЦО-11;

Также плата ЦО-12 обеспечивает поиск состояния циклового синхронизма при включении блока АЦО-11. Коэффициент накопления по входу в синхронизм = 2; среднее время вхождения в состояние циклового синхронизма не более 2мс; коэффициент накопления по выходу из синхронизма = 4.

Рисунок 1

Рассмотрим подробно работу приёмника циклового синхросигнала ЦСП ИКМ-30(см. рис. 1). Многоканальный цифровой сигнал ИКМ и тактовая частота 2048кГц поступают с выходов платы BC-11 на входы восьмиразрядного последовательного регистра приёмника синхросигнала. С выходов регистра многоканальный цифровой сигнал в параллельном коде поступает на входы опознавателя.

Опознаватель осуществляет выделение из принятого сигнала синхрокомбинации вида 0011011. Вход опознавателя подключен к входам накопителей по входу и выходу, а также ко входу формирователя сигнала установки.

Накопитель по выходу представляет собой четырёхразрядный сдвиговый регистр, и сигнал с выхода опознавателя записывается в этот регистр с частотой 4кГц. Процесс записи формируется сигналом, формируемым счётчиком-делителем на 512, на вход которого поступает сигнал тактовой частоты 2048кГц.

При наличии циклового синхронизма все триггеры сдвигового регистра накопителя по выходу находятся в состоянии, соответствующему приёму четырех последовательно поступивших синхрокомбинаций. Если синхронизм по какой-либо причине потерян, в сдвиговый регистр накопителя по выходу записывается информация об отсутствии синхрокомбинации на должном месте, и, при накоплении четырёх сигналов об отсутствии синхрокомбинаций, на выходе накопителя по выходу появляется сигнал об отсутствии синхронизма, поступающий на вход формирователя сигнала установки и на вход устройства контроля.

Сигнал с выхода опознавателя записывается также в двухразрядный сдвиговый регистр накопителя по входу, частота записи 4кГц, но, в отличие от накопителя по выходу, сигнал записи формируется дополнительным счётчиком, аналогичным счётчику-делителю на 512.

При синхронной работе ЦО-12 счётчик-делитель на 512 и дополнительный счётчик работают синфазно, однако, при потере синхронизма, первая неправильно принятая синхрокомбинация (точнее отсутствие её на должном месте) вызывает процесс поиска синхронизма. При поиске синхронизма дополнительный счётчик останавливается, и на вход накопителя по входу поступает тактовая частота 2048кГц. Накопитель по входу анализирует выходной сигнал опознавателя, и, при поступлении на вход опознавателя синхрокомбинации, разрешает работу дополнительного счетчика. Через цикл (256 тактов с частотой 2048кГц) производится анализ на позиции Р2 принятой кодовой комбинации.

Если этот сигнал не равен «логической единице», то дополнительный счётчик сбрасывается, и процесс поиска начинается заново; в противном случае накопитель по входу анализирует выход опознавателя через два цикла после приёма синхрокомбинации. Правильно принятая синхрокомбинация означает, что дополнительный счётчик работает синхронно с принимаемым многоканальным цифровым сигналом.

После того, как накопитель по выходу зафиксирует выход из синхронизма, а накопитель по входу фиксирует нахождение нового положения синхросигнала, формирователь сигнала установки (при получении сигнала с выхода опознавателя) сформирует импульс, устанавливающий счётчик-делитель на 512 в нужную фазу и синхронизм ЦО-12 восстанавливается. Функциональная схема приёмника циклового синхросигнала аппаратуры ИКМ-30С-4 находится в приложениях(приложение №2).

САПР МАХ+plusII фирмы ALTERA

САПР MAX+plusII представляет собой архитектурно независимую среду проектирования, которая легко приспосабливается к конкретным проектным требованиям и может работать на различных компьютерных платформах. MAX+plusII предоставляет различные способы ввода проекта, быструю компиляцию и непосредственное программирование микросхем.

MAX+plusII предоставляет полный спектр возможностей для проектирования цифрового устройства: ввод проекта(различными способами), логический синтез, компиляцию с заданными временными ограничениями, функциональное и временное моделирование, разделение проекта на части и моделирование проекта, выполненного на нескольких микросхемах, временной анализ, автоматическое определение ошибок, программирование и верификацию микросхем. САПР MAX+plusII позволяет вводить и сохранять проекты в виде файлов AHDL(язык описания аппаратуры фирмы Altera), EDIF, Verilog HDL, VHDL, OrCAD.

MAX+plusII состоит из 11 полностью интегрированных программных модулей, каждый из которых выполняет свою функцию при создании проекта. Ввод проекта может осуществляться следующими способами: с помощью графического редактора(составление принципиальной схемы из заранее заготовленных символов путём соединения выводов), с помощью текстового редактора(ввод описания проекта на одном из выше перечисленных языков), а также с помощью редактора временных диаграмм. Проект MAX+plusII может содержать в себе различные типы файлов.

В данном проекте использовались графический и текстовый редакторы. Редактор временных диаграмм применялся исключительно для симуляции и отладки проекта.

Работа над проектом

В связи со сложностью поиска зарубежных аналогов отечественным микросхемам, применяемым в ИКМ-30, в библиотеках MAX+plusII, был выбран путь реализации этих микросхем с помощью текстового редактора.

На языке AHDL были описаны только те элементы функциональной схемы, для которых не нашлось точных аналогов в серии 74. Такими элементами были выбраны: входной семиразрядный сдвиговый регистр(INPUT_Register); опознаватель, представляющий собой элемент 7И-НЕ с инверсиями на некоторых входах(DECODER); накопитель по входу(In_Case); дополнительный счётчик и счётчик-делитель на 512(Count512). Для написания программ, описывающих работу элементов, были использованы стандартные элементы кода AHDL Templates. Листинги этих программ находятся в приложениях. Накопитель по выходу строился путём добавления дополнительной логики к уже существующему библиотечному регистру.

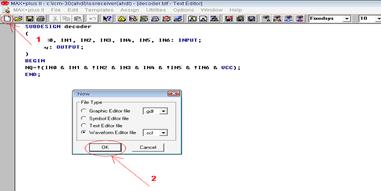

Все вновь созданные элементы были откомпилированы и проверены на симуляторе MAX+plusII. Для этого, при открытом файле программы(*.tdf):

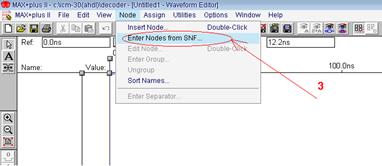

При последовательном нажатии указанных кнопок происходит проверка на ошибки, автоматический выбор микросхемы, компиляция в код ассемблера этой микросхемы, симуляция в симуляторе MAX+plusII. Перед симуляцией необходимо создать файл *.scf с аналогичным именем, что и *.tdf, который будет описывать на какие выводы вновь созданного элемента какие сигналы подавать при симуляции. Этот файл создаётся в редакторе временных диаграмм, который позволяет подавать сигналы любой структуры. Для создания файла *.scf:

Теперь необходимо добавить выводы:

Редактирование сигналов производится следующим образом. Необходимо выбрать вывод и при нажатой левой кнопке мыши выбрать редактируемый участок. Затем с помощью панели инструментов(слева) установить нужный уровень сигнала.

Описание элементов схемы

Input_Register представляет собой сдвиговый регистр, состоящий из 7 D-триггеров, соединенных последовательно. ИКМ сигнал подаётся на информационный вход триггера младшего разряда, а снимается в параллельном коде с выходов всех триггеров одновременно. Особенностью этого регистра является то, что он работает по заднему фронту сигнала тактовой частоты, которая подаётся на clk входы всех триггеров.