Курсовая работа: Моделирование работы приемника циклового синхросигнала аппаратуры ЦСП

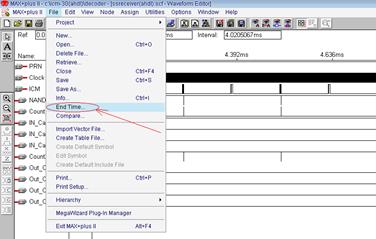

Задаём конечное время симуляции 5мс:

Задаём тестовые сигналы на входах:

PRN – устанавливаем в 1 и добавляем единичный сброс в 0 длительностью в 1 синхроимпульс в самом начале диаграммы.

Clock – сигнал тактовой частоты с периодом 488нс(частотой 2048кГц)

ICM – создаём сигнал ИКМ в соответствии с временными интервалами реальной системы. Можно создать чётный и нечетный цикл а потом размножить по всей длине диаграммы. Сигнал ИКМ необходимо сдвинуть относительно начала диаграммы на время, достаточное для достижения устойчивого состояния схемы при включении(в противном случае возникают неопределенности).

Запускаем симуляцию и анализируем результат.

Сначала мы подаём идеальные сигналы, что должно соответствовать состоянию циклового синхронизма. Схема при начале симуляции находится в состоянии рассинхронизации потому, что ИКМ сигнал смещен: дополнительный счётчик находится в режиме поиска синхронизма, а счётчик-делитель на 512 работает в режиме деления частоты, но при этом считает с момента появления сигнала тактовой частоты, а не с момента прихода первой синхрокомбинации(см. приложение №5). Накопитель по выходу фиксирует отсутствие синхронизма и записывает последовательно в течение пяти циклов единицы. Накопитель по входу работает в режиме поиска нового положения синхропоследовательности. При первом же правильно принятом синхросигнале записывает 1 на выход младшего разряда, дополнительный счётчик переходит в режим деления на 512 и теперь только через 256 тактов под действием тактового импульса с выхода S счётчика проверяется наличие 1 в Р2 КИ0 нечетного цикла, единица присутствует, накопитель по входу не меняет своего состояния. В следующем цикле происходит запись 1 в следующий разряд накопителя по входу, сбрасывается счётчик-делитель на 512 и начинает работать в фазе с приходящим ИКМ сигналом. В следующем цикле опять проверяется наличие единицы на месте Р2 и накопители не меняют своего состояния. При приходе синхрокомбинации в пятом по счёту цикле происходит обнуление всех триггеров накопителя по выходу и окончательное заполнение единицами накопителя по входу. Схема вошла в синхронизм с ИКМ сигналом через 4 полных цикла. Далее изменений нет, т.к. сигналы поступают синхронно без воздействия помех и схема находится в синхронизме.

Теперь внесем в сигнал ИКМ искажения после того момента как схема найдёт первоначальный синхронизм. Занулим третий бит синхропоследовательности в 6 цикле (см. приложение №6). При таком искажении сигнала схема из состояния синхронизма перешла в состояние поиска синхронизма, дополнительный счётчик остановился и выдаёт на выход сигнал тактовой частоты, что продолжается до прихода правильной синхропоследовательности в цикле 8. Через 3 такта накопитель по входу заполнился нулями. Счётчик-делитель на 512 остаётся в фазе с ИКМ сигналом и продолжает считать, но в накопитель по выходу записалась единица. Эта единица остаётся в накопителе до момента прихода правильной синхропоследовательности в восьмом цикле. В цикле 7 происходит проверка Р2, но там нет искажений, сигнал верный и накопители остаются в прежнем состоянии. При приходе правильной синхропоследовательности в цикле 8 дополнительный счётчик переходит в режим деления на 512, в накопитель по входу записывается 1, накопитель по выходу сбрасывается. Синхронизм восстановлен.

Исправим сигнал ИКМ и внесем искажение в цикле 7. Занулим Р2 (см. приложение №7). При проверке Р2 КИ0 седьмого цикла схема не обнаруживает единицы. Накопитель по входу сбрасывается в 0(все разряды), дополнительный счётчик переходит в режим поиска синхронизма. Накопитель по выходу в прежнем состоянии. При приходе правильной синхрокомбинации в восьмом цикле в младший разряд накопителя по входу записывается единица, дополнительный счётчик переходит в режим счёта, в накопитель по выходу записывается единица в младший разряд. Накопитель по выходу сбрасывается только в цикле 10. И синхронизм снова восстановлен.

Теперь снова исправим сигнал ИКМ и внесем изменения в сигнал тактовой частоты после момента нахождения первоначального синхронизма. Удалим один импульс (см. приложение №8). Искажение внесено в четвертом цикле. На пятом цикле ничего не происходит, т.к. Р2 КИ0 смещается из-за искажения на одну позицию вправо на Р3, а там тоже единица и схема принимает её за верное значение. А вот на цикле 6 происходит срыв синхронизма из-за того, что счётчики срабатывают не в момент прихода синхропоследовательности, а с запаздыванием на 1 такт. Накопитель по входу работает также как при искажении в синхропоследовательности (в режиме поиска) до прихода правильной синхропоследовательности в восьмом цикле. Там происходит перевод дополнительного счётчика в режим счёта и в накопитель по входу записывается единица. Но счётчик-делитель на 512 по прежнему не в фазе и в накопитель по выходу на восьмом цикле записывается еще одна единица (вторая). Накопитель по выходу сбросится только на десятом цикле, когда счётчик-делитель будет установлен в фазу. После этого момента синхронизм можно считать восстановленным.

Итак, проведен анализ работы схемы приёмника циклового синхросигнала при единичных искажениях во входных сигналах. Теперь проанализируем работу схемы в режиме аварии циклового синхронизма. Исказим сразу три цикла сигнала ИКМ. Занулим: Р3 КИ0 шестого цикла, Р2 КИ0 седьмого цикла, Р3 КИ0 восьмого цикла (см. Приложение №9). В шестом цикле происходит срыв синхронизма. Дополнительный счётчик переходит в режим поиска, накопитель по входу обнуляется за три такта, в накопитель по выходу записывается единица. При приходе неправильной синхрокомбинации в цикле 8 накопитель записывает еще одну единицу, накопитель по входу и дополнительный счётчик в прежнем состоянии. Т.к. в девятом цикле сигнал соответствует верному, JK-триггер сброса накопителя по выходу устанавливается в соответствующий режим и на десятом цикле происходит сброс накопителя по выходу. Синхронизм будет восстановлен только в двенадцатом цикле. Это сделано для того, чтобы исключить возможность ложного синхронизма из-за формирования ложных синхрогрупп. Схема проверяет три цикла подряд и тогда, если все в порядке, можно считать, что синхронизм восстановлен.

Итак, промоделированы возможные причины потери синхронизма, схема проекта работает исправно. Теперь можно файл проекта прошить в реальную микросхему, которая будет выполнять функции приемника циклового синхросигнала.

Выводы

В ходе данной работы я изучил на практике работу приёмника циклового синхросигнала аппаратуры ЦСП ИКМ-30С-4, а также структуру цикла передачи. Также я познакомился с современными способами разработки цифровой аппаратуры, а в частности с системой автоматизированного проектирования MAX+plusII фирмы Altera, как в плане проектирования, так и в плане проверки схемы на работоспособность.

Литература

Л.С. Левин, М.А. Плоткин «Цифровые системы передачи информации»Радио и Связь 1982г. Москва

Руководство по эксплуатации цифровой системы передачи информации ИКМ-30-С-4:

Комплект оборудования №1 Аппаратура первичной цифровой системы передачи для СТС ИКМ-30С-4 Альбом №1

Комплект оборудования №1 Блок АЦО-11 Альбом №13

Комплект оборудования №1 Блок АЦО-11 Альбом №14