Курсовая работа: Моделирование работы приемника циклового синхросигнала аппаратуры ЦСП

In_Case – сдвиговый регистр, состоящий из трёх D-триггеров. Работает по переднему фронту сигнала синхронизации, поступающему с дополнительного счётчика. Имеет вход асинхронной установки в 1 с активным уровнем LOG«0». Особенность: выходы разрядов инвертированы.

Count512 – восьмиразрядный счётчик со сложной структурой. Включает семиразрядный счётчик и дополнительный триггер. При переполнении семиразрядного счетчика выдаётся промежуточный сигнал BR, который и передаётся на выход, но через логическую схему, объединяющую его элементами И с выходными сигналами(прямым и инверсным) дополнительного триггера. Счётчик имеет асинхронную установку. Если на входе R LOG0, то счётчик делит тактовую частоту на 512 и выдаёт 4кГц, если на R LOG1, то счётчик выдаёт на выход сигнал тактовой частоты.

Out_Case – четырёхразрядный последовательно-параллельный регистр, параллельные входы которого соединены с общей шиной, а последовательный вход с шиной питания. Вход MODE выбирает режим работы(параллельная загрузка или сдвиг), в следствие чего изменяя MODE мы можем либо записывать последовательно LOG1 либо сбрасывать все триггеры регистра в 0.

С помощью D-триггера на входе асинхронной установки In_Case мы сбрасываем накопитель по входу в нужный момент. На нём организована проверка Р2 КИ0 нечетных циклов.

RS триггер выбирает режим работы дополнительного счётчика(деление на 512 или сброс и выдача тактовой частоты).

Элемент 4И-2ИЛИ-НЕ формирует сигнал установки счётчика-делителя на 512 в момент, когда накопитель по выходу зафиксировал выход из синхронизма, а накопитель по входу обнаружил новое место синхропоследовательности и есть сигнал отклика от опознавателя.

JK-триггер проверяет Р2 КИ0 нечетных циклов и выбирает режим записи для накопителя по выходу.

Счётчики работают по переднему фронту сигнала тактовой частоты, накопитель по выходу по заднему.

С 0 разряда накопителя по выходу выдаётся информация об ошибках. Третий разряд выдаёт сигнал о потере циклового синхронизма «Авария ЦС»

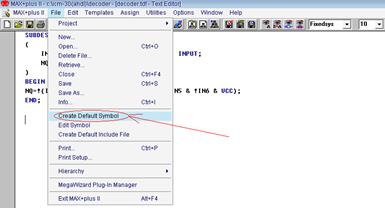

Для дальнейшего соединения элементов необходимо создать файлы символов (для каждого). Это делается следующим образом: открываем файл описания, а затем

Файл символа описывает графическую структуру элемента: имя, количество выводов, их наименование. Для библиотечных элементов эти файлы уже существуют.

Сборка проекта

Для сборки проекта из заготовленных элементов воспользуемся графическим редактором MAX+plusII.

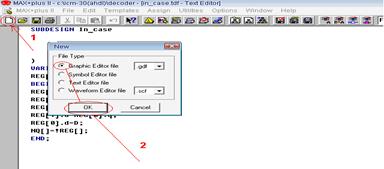

Создадим графический файл *.gdf:

Добавлять элементы можно двойным щелчком на пустом пространстве. При этом появляется окно, в котором необходимо выбрать библиотеку и элемент или просто ввести имя элемента.

Когда все элементы размещены, нужно их соединить согласно схеме. Эта операция проводится точно так же как в любом графическом редакторе. Просто рисуем линии проводников. Однако большое количество проводников загромождает рабочее пространство. Чтобы это исключить в MAX+plusII используется привязка с помощью имён. В данном проекте этот приём тоже использован. Два проводника называются одинаково и они уже соединены. Т.е. проводники могут находиться в разных углах экрана и не соединяться графически.

Для того, чтобы проект был скомпилирован необходимо указать компилятору куда подавать входные и откуда снимать выходные сигналы. Для этого нужно добавить элементы INPUT и OUTPUT из стандартной библиотеки.

Теперь схема собрана. Для компиляции используем приём описанный выше. Схема приёмника циклового синхросигнала готовая для моделирования в симуляторе MAX+plusII находится в приложениях.

Моделирование работы схемы проекта

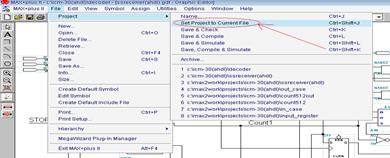

Чтобы выяснить правильно ли работает схема, её необходимо промоделировать. Воспользуемся редактором временных диаграмм MAX+plusII. Создаём файл *.scf точно так же как это делалось для каждого из элементов. Необходимо проинициализировать проект(определить какой из файлов будет главным в проекте). Для этого выбираем файл схемы *.gdf и:

Сохраняем файл *.scf под тем же именем, что и проект(в данном случае ssreceiver). Добавляем необходимые выводы на временную диаграмму: PRN, Clock, ICM, NAND7, Count1, In_Case[0..2], Count2, Out_Case[0..3].

PRN – сигнал предварительной установки триггеров

Clock – сигнал тактовой частоты 2048кГц

ICM – сигнал, в соответствии со структурой реального сигнала ИКМ

NAND7 – сигнал с выхода опознавателя

Count1, Count2 – сигналы с выходов дополнительного счётчика и счётчика-делителя на 512 соответственно.