Курсовая работа: Преобразование параллельного двоичного кода в код Хэмминга

Рисунок 4 – Функциональная электрическая схема кодера кода Хэмминга

Таким образом, кодер состоит из четырёх сумматоров по модулю два, выходы которых соответствуют четырём проверочным символам. В функциональной схеме кодера используется параллельный интерфейс (совокупность средств и методов взаимодействия между элементами системы) ввода и вывода данных. Если один из проверочных символов равен единицы, то в данном канале присутствует ошибка, и, глядя на проверочные уравнения, можно сказать, в каком именно разряде произошла ошибка, если же равно нулю, то ошибки нет в канале информации. В соответствии на выходе кодера формируется наше сообщение (а1..а8) и проверочные символы (а9..а12).

5. РАЗРАБОТКА ПРИНЦИПИАЛЬНОЙ ЭЛЕКТРИЧЕСКОЙ СХЕМЫ

КОДЕКА

5.1 ОБОСНОВАНИЕ ВЫБОРА ЭЛЕМЕНТНОЙ БАЗЫ

С целью минимизации веса, габаритов и объема оборудования кодера принципиальная схема кодера выполняется с использованием современных интегральных микросхем (ИМС).

Номенклатура выпускаемых интегральных микросхем обширна. Для построения устройств автоматики и вычислительной техники широкое применение находят цифровые микросхемы, которые изготавливают по стандартной технологии биполярных микросхем транзисторно-транзисторной логики (ТТЛ).

При выборе элементной базы, т.е. конкретной серии и типа ИМС, для разработки принципиальной схемы кодера кода Хэмминга необходимо, чтобы выполнялись следующие условия:

- потребление кодеком электроэнергии должно быть минимальным;

- ИМС должны иметь высокую степень интеграции, что обеспечит минимальный объем оборудования кодека;

- минимальная стоимость ИМС;

- ИМС должны обеспечивать надежную работу кодека и др.

В данной работе выбраны микросхемы серии К555. Отличие их от микросхем серии К155 – использование транзисторов с коллекторными переходами, зашунтированными диодами Шотки. В результате транзисторы микросхем серии К555 не входят в насыщение, что существенно уменьшает задержку выключения транзисторов. К тому же они значительно меньших размеров, что уменьшает емкости их р-n-переходов.

5.2 РАЗРАБОТКА ПРИНЦИПИАЛЬНЫХ СХЕМ ФУНКЦИОНАЛЬНЫХ БЛОКОВ КОДЕРА

Распишем функциональные блоки для построения принципиальной схемы преобразования параллельного двоичного кода в код Хэмминга.

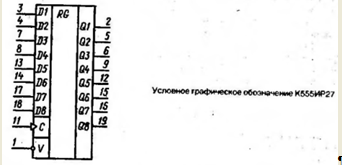

Код параллельно поступает на информационные входы регистра, который представляет собой линейку из триггеров и применяется для накопления (хранения) и сдвига данных. В данном случае используется восьмиразрядный регистр с разрешением записи К555ИР27. Его условное графическое обозначение представлено ниже

1 – вход разрешения записи; 2 – выход информационный первого разряда; 3 – вход информационный первого разряда; 4 – вход информационный второго разряда; 5 – выход информационный второго разряда; 6 – выход информационный третьего разряда; 7 – вход информационный третьего разряда; 8 – вход информационный четвёртого разряда; 9 – выход информационный четвёртого разряда; 12 – выход информационный пятого разряда; 13 – вход информационный пятого разряда; 14 – вход информационный шестого разряда; 15 – выход информационный шестого разряда; 17 – вход информационный седьмого разряда; 18 – вход информационный восьмого разряда; 19 – выход информационный восьмого разряда.

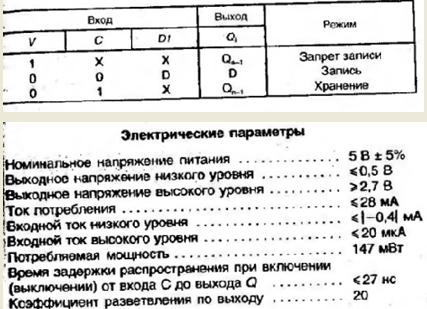

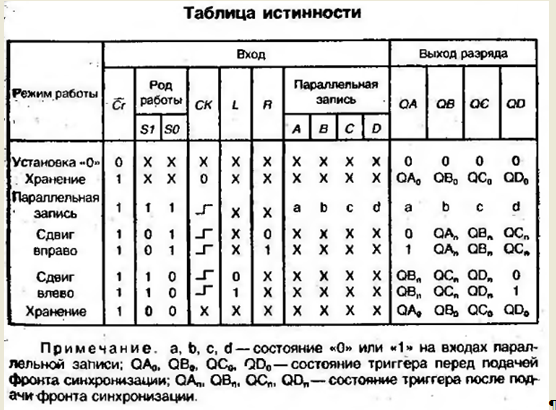

Таблица истинности К555ИР27

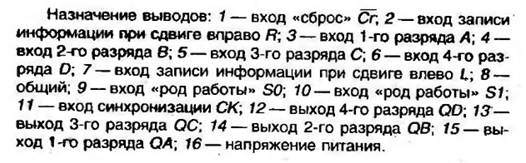

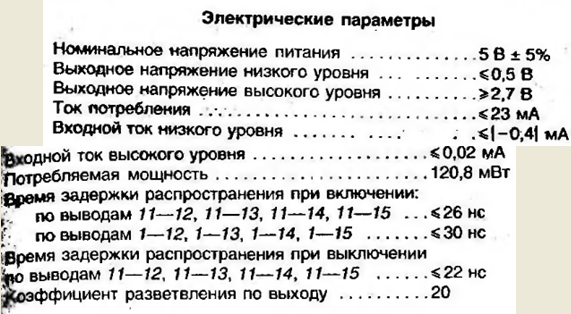

В итоге информационные и сформированные проверочные символы поступают на ряд регистров (3), на выходе получаем параллельный код. В этом случае используются четырёхразрядные универсальные регистры К555ИР11А.

Условное графическое обозначение К555ИР11А

Для построения принципиальной схемы блока формирования проверочных символов (БФПС) используются сумматоры серии К555ИМ5. Микросхема представляет собой два одноразрядных полных сумматора.

Условно-графическое изображение