Курсовая работа: Расчет буквенно-цифрового дисплея

–Напряжение источника питания,В 5

–Временная задержка распред. сигнала, нс 21

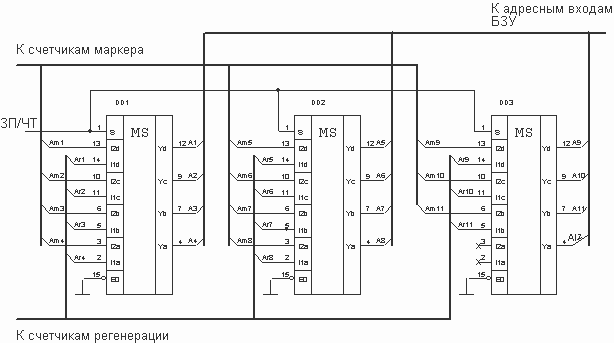

Рисунок 3 – Принципиальная электрическая схема мультиплексора

5 Расчет ПЗУ знакогенератора

Для хранения информации о графике каждого знака требуется 7 ячеек памяти с разрядностью 10.

В связи с тем, что число адресуемых ячеек памяти должно быть кратно степени 2, на каждый знак приходится 2пу ячеек памяти.

Определим число ячеек памяти ПЗУ, необходимое для размещения в нем всех знаков алфавита:

Необходимая информационная ёмкость ПЗУ:

![]() ,

,

где ![]() — разрядность адресных входов, необходимая для адресации рядов матрицы знака.

— разрядность адресных входов, необходимая для адресации рядов матрицы знака.

![]() ,

,

![]() .

.

![]()

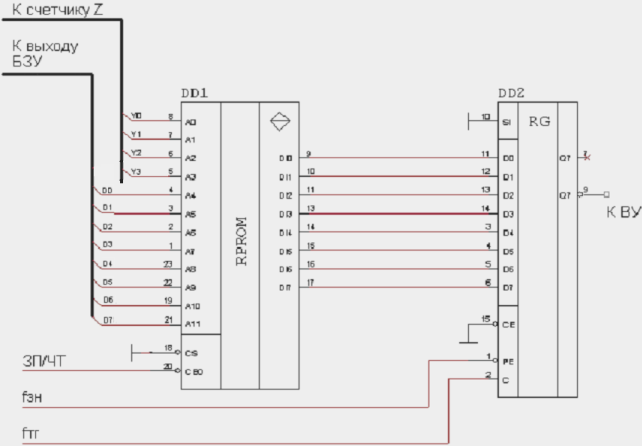

В качестве ПЗУ выбираем электрически программируемую БИС КР1656РЕ3.

| Справочные данные микросхемы: | |

| Информационная ёмкость: | С = 32768 бит |

| Организация: | 4k´8 |

| Время выборки относительно адреса | tВА не более 50 нс |

| Напряжение питания | UСС = +5 В ± 5 % |

| Ток потребления | Iпот = 90 мА |

Для полноценной работы знакогенератора достаточно одной микросхемы ПЗУ КР1656РЕ3.

Количество знаков, которое можно разместить в выбранную БИС:

![]() .

.

Таким образом, выбранная БИС удовлетворяет заданию, так как ![]()

6 Выбор регистра знакогенератора

Так как разрядность сдвигового регистра должна быть не менее b’З =8, то в качестве регистра выбираем восьмиразрядный знаковый регистр К555ИР9, имеющий параллельные и последовательные входы. Параллельно данные загружаются в регистр через входы D0-D7 асинхронно, если на вход разрешения параллельной загрузки РЕ подается напряжение низкого уровня. Если на входе РЕ присутствует напряжение высокого уровня, то данные вводятся в регистр через последовательный вход S1. Сдвиг данных вправо на одну позицию происходит согласно каждому положительному перепаду тактового импульса на входе С . Вход разрешения тактовым импульсам СЕ имеет активный низкий уровень. Регистр имеет комплиментарные выходы Q7 и Q7. Микросхема К555ИР9 потребляет ток 63 мА.

Рисунок 4 – Принципиальная электрическая схема знакогенератора

7 Выбор компаратора

Компараторы кодов служат для сравнения двух многоразрядных двоичных слов. В разрабатываемом устройстве отображения информации компаратор формирует единичный сигнал при равенстве кодов с выхода счетчиков регенерации и счетчиков маркера.

Применим четырехразрядный компаратор кодов К555СП1 – микросхему средней степени интеграции. Требуется построить 12-разрядный компаратор, следовательно, будет использоваться 4 микросхемы К555СП1 (последовательный режим наращивания). Время задержки сигнала одной микросхемой – 15 нс, следовательно, составной 11-разрядный компаратор задерживает сигнал на 45 нс.:

![]() ,

,

где ![]() – время задержки распространения сигнала одним компаратором;

– время задержки распространения сигнала одним компаратором;

n – количество микросхем.