Курсовая работа: Разработка узла компаратора регулятора напряжения

а) б)

Рисунок 2.1 – Стабилизатор напряжения.

Выполнение этого условия для схемы на рисунке 2.1 (а) приведет к десятикратному увеличению тока I0, который является током потребления компаратора.

Рассчитаем значение R1 для схемы выбранного стабилизатора (рисунок 2.1 (б)). Напряжение. выдаваемое стабилизатором равно:

![]() (2.2)

(2.2)

где: VB — напряжение пробоя стабилитрона,

VBE — прямое падение напряжения на переходе Б – Э n – p – n транзистора.

Типовое значение VB = 6,5В (RSB = 100Ом/□), VBE = 0,7В. Подставляя в (2.2) получим:

![]()

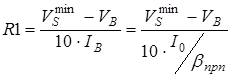

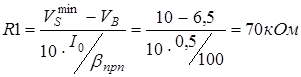

Значение R1 определяется из условия (2.1):

(2.3)

(2.3)

где: ![]() — минимальное напряжение питания,

— минимальное напряжение питания, ![]() =10В,

=10В,

I0 — выходной ток стабилизатора, I0 ![]() 500мкА,

500мкА,

Βnpn — коэффициент усиления (ОЭ) n – p – n транзистора, Βnpn = 100.

Отсюда:

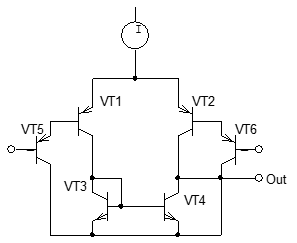

Компаратор напряжения должен оценивать близкое к нулю напряжение, поэтому выберем схему компаратора, входное напряжение которого включает нулевой потенциал (рисунок 2.2) [Л4].

Рисунок 2.2 – Компаратор напряжения.

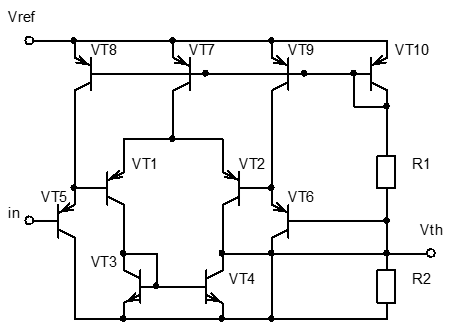

Для более надежного запирания транзисторов VT1 и VT2, к их базам подключим источники тока.

Рисунок 2.3 – Компаратор напряжения с источником тока.

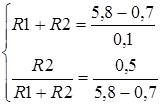

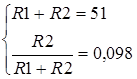

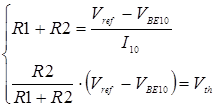

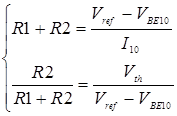

Рассчитаем источник тока для компаратора. Источником тока будет являться токовое зеркало на p – n – p транзисторах (рисунок 2.3) [Л5]. Учитывая, что ток потребления всей схемы не должен превышать 350мкА, выберем ток через токозадающую цепь (транзистор VТ10) равным 100мкА. Ток для питания компаратора выберем равным: 0,6 I10 = 60мкА, токи через VТ8 и VТ9 выберем равными: 0,2 I10 = 20мкА. Для уменьшения тока потребления схемы, цепочка токозадающих резисторов в цепи транзистора VТ10 будет являться делителем напряжения, служащим для организации порога срабатывания компаратора (Vth). Исходя из этого запишем систему уравнений для нахождения R1 и R2:

(2.4)

(2.4)

(2.5)

(2.5)

где: Vth — порог срабатывания компаратора.

Подставляя значения в (2.5) получим: