Курсовая работа: Реализация устройства обработки информации

0

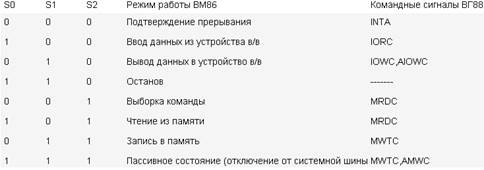

Реж.

1

Реж.

2

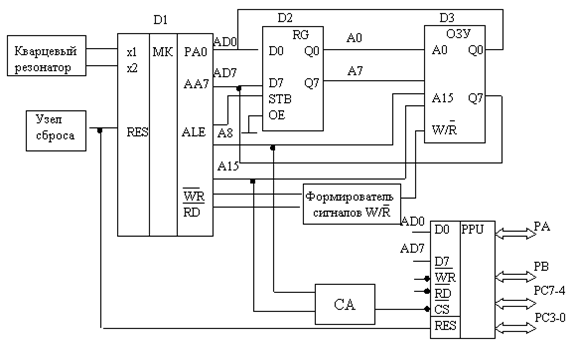

1.2 Структурная схема устройства

Система состоит из микроконтроллера i8086, порты которого используются для вывода адреса ОЗУ, подключен адаптер параллельного интерфейса i8255. Взаимодействие микроконтроллера с внешней памятью и периферийными устройствами осуществляется по шине адреса. Данные передаются и принимаются микроконтроллером по шине данных. Управляющие сигналы передаются по шине управления.

ОЗУ подключены своими адресными входами к шине адреса и передают и принимают данные по шине данных. Адрес формируется на контактах портов РА – 8 младших разрядов и РС – старшие разряды. Обмен данными с ОЗУ микроконтроллер осуществляет через порт РА. Поэтому младшие разряды адреса на время обмена сохраняются на время обмена в регистре-защелке.

Структурная схема устройства приведена ниже на рис.1.

Рис.1 Структурная схема системы

1.3 Описание микроконтроллера i8086

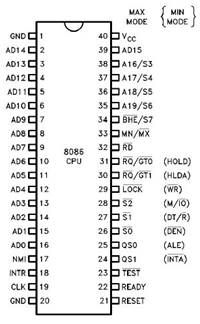

Схема цоколевки микроконтроллера i8086 приведена на рис.2

Рис. 2 Условное графическое обозначение микроконтроллера i8086

Шестнадцатиразрядный однокристальный МП выполняющий около 2 млн. операций в секунду. Синхронизируется тактовой частотой 25 МГЦ. Имеет 20-ти разрядную шину адреса, что позволяет обеспечить прямую адресацию 1 Мбайт внешней памяти. Область адресного пространства памяти разбита на сегменты по 64 Кб. Такая организация памяти обеспечивает удобный механизм вычисления физических адресов. ША и ШД мультиплексированы. При организации вычислительных систем их нужно разделить (регистры-защелки). МП может обращаться как к памяти, так и к внешним устройствам. При обращении к внешним устройствам используются 16 младших линий ША. Следовательно можно подключить 64 К 8-битных внешних устройств, либо 32 К 16-ти разрядных. МП имеет многоуровневую систему прерываний: 256 векторов прерываний. Данный МП является дальнейшим совершенствованием К580ВМ80. Система команд сходна, но более расширена. Программное обеспечение легко переводится с одного МП на другой.

Наименование выводов i8086:

NMI – запрос на немаскируемое прерывание

INTR – запрос на маскируемое прерывание

CLK – выход ГТИ для управления памятью

RESET – сигнал системного сброса

READY – выход готовности генератора

TEST – проверочный вход, используется в команде WAIT для организации холостых тактов: «1» - МП выполняет «0», с периодичностью 5 Т проверяет состояние этого сигнала

S0-S2 – предназначены для подключения к центральному микропроцессору

LOCK – вход запрета освобождения системной шины: «1» - арбитру запрещается освобождать системную шину, не зависимо от его приоритета

RQ/GT – обеспечивает доступ к линии связи только одному МП. Выходы другого в этот момент находятся в 3-м состоянии. Дешифратор адреса определяет адрес всей конкретной схемы

RD – чтение

MN/MX – минимальный / максимальный режимы, определяющие конфигурацию вычислительной системы. MN- ограничение объема памяти и т.д.