Курсовая работа: Реализация устройства обработки информации

AD0-AD15 – мультиплексированная шина адреса/ данных

A16/S3-A19/S6 – мультиплексированные линии адреса состояния

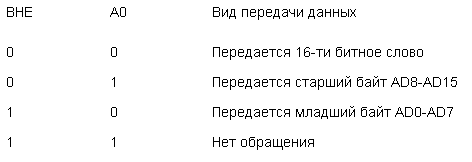

BHE – разрешение старшего байта. Работает совместно с сигналом А0, обеспечивая механизм передачи информации по ШД

DEN - строб сопровождения данных для фиксации в регистры-защелки

ALE – строб сопровождения адреса в регистр-защелку

INTA – системный сигнал подтверждения прерывания

Vcc – вывод источника питания

Основные технические характеристики:

· Тактовая частота От 0 до 5 МГц (i8086)

· Разрядность регистров: 16 бит

· Разрядность шины данных: 16 бит

· Разрядность шины адреса: 20 бит

· Объём адресуемой памяти: 1 Мбайт

· Количество транзисторов: 29 000

· Техпроцесс (нм): 3000 (3 мкм)

· Площадь кристалла (кв. мм): ~30 (по другим данным, 16 мм²)

· Максимальное тепловыделение: 1,75 Вт

· Разъём: нет (микросхема припаивалась к плате)

· Поддерживаемые технологии: 98 инструкций

· Диапазон напряжения питания:

- от 2,7 до 5,0 В (i8086)

· Корпус: 40-контактный керамический DIP

2. Разработка и описание схемы

2.1 Процессорный блок

Процессорный блок состоит из микроконтроллера i8086, регистра защелки младшей части адреса RG. Адрес формируется на выходе портов РА – младшая часть adr(0..7) на внутренней шине AdrDat, которая попадает на системную шину адреса после регистра защелки Adr, и РС – старшая часть, которая непосредственно подается на системную Adr - разряды adr(8..15). Обмен данными с памятью и внешними устройствами, осуществляется как по внутренней шине Dat, которая совмещена с шиной младшей части адреса и подключена к порту РА dat(0..7)=adr(0..7), так и по порту РС.

Сигнал ALE является сигналом защелкивания младшей части адреса в регистр RG.

РD2, РD3 – линии приема запроса на прерывание по вводу данных от внешнего устройства, РD6 и РD7 – линии сигналов записи и чтения.

2.2 Расчет ОЗУ