Курсовая работа: Реализация устройства обработки информации

IDH = mc * IIDH = 2 * 2 = 4 мА

CD = mc * CID + Cm = 2 * 5 + 20 = 30 пФ

где IIDL , IIDH - входные токи логического 0 и логической 1 по информационным цепям выбранной БИС ОЗУ. CID - входная емкость по информационному входу БИС ОЗУ.

Определяем токи нагрузки и емкостную нагрузку для схем ввода адреса по адресным цепям БИС ОЗУ по формулам:

IAL = m * IIAL = 2 * 3,2 = 6,4 мА

IAH = m * IIAH = 2 * 2 = 4 мА

CA = m * CIA + Cm = 2 * 5 + 20 = 30 пФ

где IIАL , IIAH - входные токи логического 0 и логической 1 по адресным цепям выбранной БИС ОЗУ. CIА - входная емкость по адресному входу БИС ОЗУ.

Определяем токи нагрузки ICSL и ICSH и величину емкостной нагрузки СCS по цепям выбора микросхем (CS) по формулам:

ICSL = mp * IICSL = 1 * 3,2 = 3,2 мА

ICSH = mp * IICSH = 1 * 2 = 2 мА

CCS = mp * CICS + Cm = 1 * 5 + 20 = 25 пФ

где IICSL , IICSH - входные токи логического 0 и логической 1 по цепям выбора (CS) БИС ОЗУ. CСS - входная емкость по цепям выбора (CS) БИС ОЗУ.

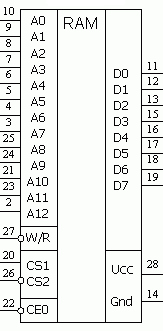

Рис. 3 Условное графическое обозначение ОЗУ К537РУ17

Наименование выводов:

A0 ÷ A12 – адресные входы.

W/R – запись/чтение.

CS1, CS2 – chip select, чип выбора.

CEO – разрешающий выход.

D0 ÷ D7 – шина данных ввода/вывода.

ОЗУ представляет собой статическое асинхронное оперативное запоминающее устройство.

Режимы работы:

| W/R | CS1 | CS2 | OE | A0..12 | D0..7 | Режим |

| Х | Н | X | X | Адрес | Данные | Хранение |

| Х | Х | L | Х | Хранение | ||

| Н | L | Н | H | Запрет выхода | ||

| Н | L | H | L | Чтение | ||

| L | L | Н | Н | Запись | ||

| L | L | Н | L | Запись |

2.3 Описание адаптера параллельного интерфейса

Адаптер параллельного интерфейса служит для расширения разрядности шины данных, а также приводит к повышению нагрузочной способности.

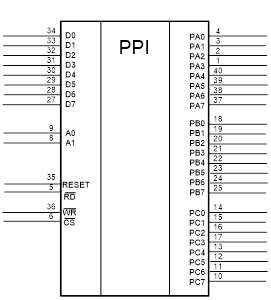

Адаптер параллельного интерфейса i8255 имеет три восьмиразрядных порта А, В и С с 3-м состоянием. Причем порт С разделен на две тетрады. Все три порта могут быть запрограммированы на ввод или вывод, причем каждая тетрада порта С может быть запрограммирована раздельно. Данные поступают в АПИ через шину данных D0…D7. С помощью сигнала CS осуществляется выбор кристалла, если сюда поступает низкий уровень сигнала, то порты будут установлены в 3-е состояние. А1, А0 – младшие разряды адреса, они служат для адресации внутренних регистров адаптера. Если количество линий ввода и вывода превышает возможности адаптера, то следует применить несколько адаптеров.

Рис. 4 Условное графическое обозначение АПИ i8255

Наименование выводов: