Курсовая работа: Регистровая память типа Магазин

Студент группы

Преподаватель

2005

Содержание

1. Задание на курсовой проект

2. Введение

3. Общий принцип работы памяти типа "очередь"

5. Функциональная схема блока управления

5.1 Блок формирования адреса

5.2 Блок дешифрирования адреса

5.3 Блок проверки заполнения памяти

5.4 Инкрементор

6. Функциональная схема блока регистров

7. Параметры некоторых микросхем

7.1 Счетчики

7.2 Дешифраторы

7.3 Регистры

7.4 Компаратор

8. Принципиальная схема устройства

8.1 Перечень элементов

8.2 Питание микросхем

9. Временные диаграммы

9.1 Временная диаграмма блока формирования адреса

9.2 Временная диаграмма блока дешифрирования адреса

9.3 Временная диаграмма блока проверки заполнения памяти

9.4 Временная диаграмма блока регистров

10. Расчет параметров устройства

10.1 Токи и потенциалы

10.2 Нагрузка

10.3 Потребляемая мощность

11. Заключение

Библиографический список

1. Задание на курсовой проект

Разработать структурную, функциональную и принципиальную схемы для устройства регистровой памяти типа "магазин".

Выполнить необходимые расчеты для обеспечения требуемых токов и потенциалов для используемых элементов, определить временные соотношения и потребляемую мощность.

Объем памяти – 256 бит (32x8).

Элементная база КМОП.

2. Введение

В цифровой аппаратуре широко используются небольшие вспомогательные запоминающие устройства с неявно выраженной адресацией, служащие для хранения очередей и называемые иногда буферами данных. Часто их строят на основе регистровой памяти.

Часто используемым в цифровой технике буфером является буфер типа «магазин», или стек, или LIFO. В отличии от нормальной очереди здесь в качестве первого кандидата на обслуживание выбирается то слово, которое встало в очередь последним. По такому закону заряжается патронами и освобождается в процессе работы магазин автоматического оружия, откуда и произошло одно из названий. Стековые структуры данных возникают в цифровых устройствах, когда процесс выполнения менее срочного задания прерывается более срочным и все данные, связанные с прерванной работой, засылаются на временное хранение в буфер типа «магазин». Выполнение срочного задания может быть в свою очередь прервано поступлением сверхсрочного и т.д.- и в стеке по мере погружения туда (сверху) новых и новых данных формируется очередь слов, стековый порядок извлечения которых (тоже сверху) соответствует правильной по рангу срочности очередности их обработки.

3. Общий принцип работы памяти типа "очередь"

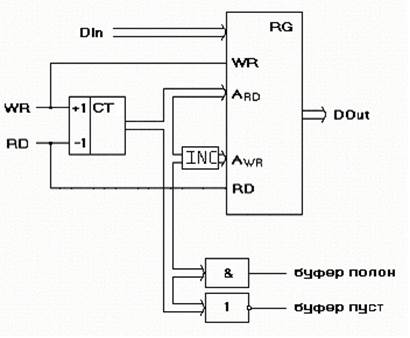

Рис. 1. Буфер типа "Магазин"

Счетчик должен быть реверсивным, т.е. уметь прибавлять 1, когда поступает команда «Заслать в стек» и вычитать 1 при команде «Извлечь из стека». При этом адрес, по которому производится засылка в стек, всегда на единицу больше адреса, по которому выполняется чтение из стека. Постоянный сдвиг на единицу адреса записи относительно адреса чтения выполняет инкрементор. Стек имеет два особых состояния: «буфер пуст» и «буфер полон». Обнаруживаются они непосредственно по нулевому и по максимальному возможному (все единицы) состоянием счетчика адреса. 4. Общая структурная схема

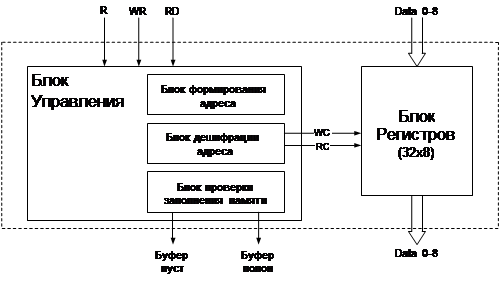

Структурная схема устройства регистровой памяти типа "магазин" представлена на рис. 2

Рис. 2. Структурная схема

Регистровая память типа "магазин" состоит из двух блоков. Блок управления предназначен для вычислений адресов записи и считывания, проверки буфера на переполнение, обнуления памяти и синхронизации с потоком данных. Входными сигналами для блока управления являются сигнал обнуления памяти, сигнал разрешения записи в память, сигнал разрешения чтения из памяти.

Блок управления в свою очередь состоит из блока формирования адреса, блока дешифрации адреса и блока проверки заполнения памяти.

Блок регистров представляет собой обыкновенный регистровый файл.

Принцип работы устройства заключается в следующем. Сигнал записи в память поступает в блок управления, по его приходу в блоке формирования адреса формируется адрес записи путем прибавления единицы к текущему адресу. Сформированный адрес поступает на вход блока дешифрации адреса. Далее по линии определяемой поступившим адресом посылается сигнал соответствующему регистру в блоке регистров о том, что на шине записи находятся данные, которые нужно записать. Данные записываются в регистр. Если при этом адрес записи становится равным максимальному адресу памяти, то выдается сигнал о том, что буфер полон.

Чтение из памяти осуществляется аналогичным методом. Сигнал чтения из памяти поступает в блок управления, по его приходу в блоке формирования адреса формируется адрес чтения. Сформированный адрес поступает на вход блока дешифрации адреса. Далее по линии определяемой поступившим адресом посылается сигнал соответствующему регистру в блоке регистров о том, что регистру пора выдать данные на шину чтения. Данные считываются из регистра. Если при этом адрес записи становится равным нулю, то выдается сигнал о том, что буфер пуст.

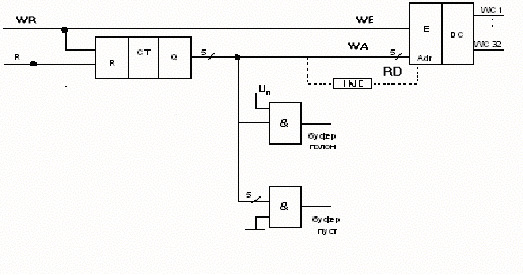

5. Функциональная схема блока управления

На рис. 3 представлена функциональная схема блока управления памятью

Рис. 3. Схема блока управления

Формирование адреса чтения показано пунктиром (то с использованием инкрементора).

Рассмотрим принадлежность элементов схемы структурным блокам

5.1 Блок формирования адреса

Блок формирования адреса состоит из реверсивного счетчика. Счетчик хранит адрес чтения и уменьшается на 1 при каждом чтении, при записи счетчик увеличивается на 1. Счетчик пятиразрядный, т.е. ведет счет от 0(00000) до 31(11111). Адрес передается по пяти адресным линиям.

Далее представлена схема реализации 5-разрядного счетчика на основе двух 4-разрядных счетчиков.

|

|

|

| ||||||

|