Лабораторная работа: Интегральные логические элементы

Основная особенность микросхем ТТЛ состоит в том, что во входной цепи используется специфический интегральный прибор – многоэмиттерный транзистор (МЭТ), имеющий несколько эмиттеров, объединенных общей базой.

Эмиттеры расположены так, что непосредственное взаимодействие между ними через участок базы отсутствует. Поэтому МЭТ можно рассматривать как совокупность нескольких независимых транзисторов с объединенными коллекторами и базами. Такой транзистор занимает меньшую площадь, а следовательно, имеет малую паразитную емкость, благодаря чему предельное быстродействие микросхем ТТЛ выше. В зависимости от сигналов на входе, МЭТ работает в прямом (нормальном) либо в инверсном (обратном) включении. МЭТ имеет существенное различие в коэффициентах передачи тока в обоих режимах. В инверсном включении, когда напряжение на эмиттерах выше напряжения на коллекторе, коэффициент передачи тока очень мал (0,005 – 0,05).

При одновременной подаче на все входы ЛЭ сигналов с уровнем больше 2,3 В все эмиттерные р-n переходы МЭТ будут находиться в закрытом состоянии. При этом через резистор R1 и многоэмиттерный транзистор в базу транзистора VT2 поступает ток, открывающий этот транзистор. Часть тока эмиттера VT2 поступает в базу транзистора VT4, который также открывается. Транзистор VT3 при этом окажется в закрытом состоянии, т.к. напряжения, действующего на его базе, недостаточно для открытия перехода база-эмиттер транзистора VT3 и диода VD5. На выходе схемы сигнал будет иметь низкий уровень, что соответствует логическому нулю. Следует иметь в виду, что в аналогичном состоянии схема будет находиться, если все входы подсоединить к источнику электропитания (+Еп) или оставить их свободными.

Если хотя бы на один из входов подать сигнал с уровнем, меньшим 0,5 В, то транзисторы VT2 и VT4 окажутся закрытыми, т. к. ток базы МЭТ переключается через соответствующий открытый эмиттерный переход во входную цепь. Транзистор VT3 при этом будет открыт, а выходной сигнал будет соответствовать логической единице (высокий уровень). Схема будет находиться в этом же состоянии, если хотя бы один из входов соединить с общим проводом или соединить с другой схемой, имеющей сигнал логического нуля на выходе.

Следует отметить, что если вход ЛЭ никуда не подключен, т.е. «висит в воздухе», то это равноценно подключению его к высокому уровню.

Если один из входов подключен к «единице», а другой – к «нулю», то ЛЭ ТТЛ будет реагировать на низкий потенциал, т. к. он имеет приоритет перед высоким потенциалом.

Микросхемы с тремя логическими состояниями

Устройства, оперирующие с дискретной информацией, при высоком уровне выходного напряжения имеют малое сопротивление между выводом «Выход» и шиной питания. В противоположном состоянии у «Выхода» малое сопротивление по отношению к общей шине. В обоих случаях выходной вывод имеет определенный электрический потенциал, который воздействует на входы последующих приборов (МС).

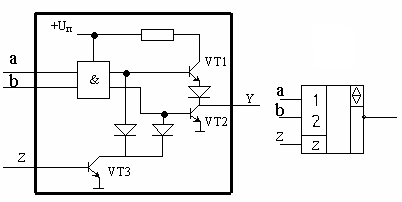

Существует категория МС, способных принимать и третье состояние, когда выход МС отключен от нагрузки. Такое состояние называют ВЫСОКОИМПЕДАНСНЫМ . Перевод МС в это состояние осуществляется по специальному входу Z. В зависимости от конкретного типа МС отключение выхода может осуществляться 1 или 0. Упрощенная электрическая схема элемента с тремя состояниями представлена на рис. 4. Когда на входе Z низкий уровень, то VT3 заперт и не влияет на работу схемы. Если Z имеет высокий уровень, то VT3 открыт и базы транзисторов VT1 и VT2 соединены с низким потенциалом (земля). Транзисторы VT1 и VT2 закрыты.

В результате связь логической части элемента с его выходом разрывается, элемент со стороны выхода приобретает высокий импеданс. Уровень потенциала на выходе неопределен (плавающий) – он может быть любым в зависимости от соотношения токов утечки VT1 и VT2. Третье состояние в отличие от 1 и 0 обозначается Z, а символ такого выхода – ромб с поперечной чертой. Элементы с 3 состояниями выхода разработаны специально для применения в качестве выходного управляемого буфера для подключения цифровых блоков к магистралям.

МС с открытым коллектором

Выходы некоторых МС выполнены так, что верхний выходной транзистор и относящиеся к нему элементы отсутствуют. Это так называемые элементы со свободным (открытым) коллектором (рис. 5).

На его выходе формируется сигнал только низкого уровня. Поэтому для нормальной работы выходного транзистора коллектор следует подключить к источнику питания через внешнюю нагрузку: резистор, элемент индикации, реле и т.п.

Для выпуска таких МС есть по меньшей мере две причины:

1. Выходной транзистор может быть использован для управления внешними устройствами, которые к тому же могут работать от других источников питания. Например, МС 155 ЛА11 позволяет под-водить к выходному транзистору до 30 В. Эти МС легко также вводить в линейный (усилительный) режим.

2. ЛЭ с открытым коллектором допускают параллельное подсоединение нескольких выходов к общей нагрузке. Такое объединение выходов называют МОНТАЖНОЙ (ПРОВОДНОЙ) ЛОГИКОЙ .

Имея дело с монтажной логикой, следует учитывать, что каждый компонент схемы утрачивает самостоятельность и действует как элемент общей системы. Так, если на одном выходе низкий потенциал, то тот же потенциал окажется на выходе всей системы. Чтобы обеспечить логическую 1 на общем выходе, необходимо иметь логические 1 на всех выходах.

Каждый из ЛЭ производит операцию И-НЕ:

![]()

![]() .

.

Следовательно:

Fвых ![]() .

.

Преобразовав последнее выражение на основе закона Де Моргана, получим:

![]() ,

,

или

![]() .

.

Из этих выражений следует, что ЛЭ с объединенными выходами функционируют подобно ЛЭ И-ИЛИ-НЕ, выполняя операцию ИЛИ-НЕ по отношению к входным переменным, связанным операциями И в каждом ЛЭ. Такое толкование послужило причиной наименования «МОНТАЖНОЕ ИЛИ». Однако для положительной логики верно «монтажное И». Схема подключения микросхем с открытым коллектором к общей нагрузке представлена на рис. 6.

Выполнение логических функций на логических элементах

Сколь угодно сложные логические функции можно реализовать с помощью набора логических элементов. Наибольшее распространение получил потенциальный способ представления информации, при котором «0» и «1» соответствует низкий или высокий уровень напряжения в соответствующей точке схемы. Сигнал сохраняет постоянный уровень (нулевой или единичный) в течение периода представления информации (такта). В цифровых устройствах все данные, необходимые для вычислений, а также результаты представляются в виде набора дискретных сигналов, принимающих одно из возможных значений «0» или «1». Преобразование цифровой информации часто осуществляется в комбинационных схемах (КС). Комбинационной называется логическая цепь, состояние которой однозначно определяется набором входных сигналов и не зависит от предыдущих состояний.

Для описания комбинационных схем используется математический аппарат булевых функций – алгебра логики. Переменные Х 1 , Х 2, …, Х n называются двоичными, если они принимают только два значения: «0» и «1». Функция от двоичных переменных Y (Х 1 , Х 2 ., Хn ) называется булевой, если она также принимает два значения «0» и «1». Связь между входными и выходными сигналами в КС аналитически описывается булевыми функциями. Существуют различные способы задания или представления булевых функций: словесное описание, табличный способ, алгебраический способ.

От таблиц истинности можно перейти к алгебраической форме представления функций. В такой форме удобно производить различные преобразования функций, например, с целью их минимизации.