Реферат: ПОСТРОЕНИЕ VERILOG-МОДЕЛИ BER-ТЕСТЕРА ДЛЯ ПРОВЕРКИ КАНАЛОВ СВЯЗИ ТЕЛЕКОММУНИКАЦИОННЫХ СИСТЕМ

Техническое задание (c вариантом решения) на курсовой проект

ПОСТРОЕНИЕ VERILOG-МОДЕЛИ BER-ТЕСТЕРА ДЛЯ ПРОВЕРКИ КАНАЛОВ СВЯЗИ ТЕЛЕКОММУНИКАЦИОННЫХ СИСТЕМ

Москва 2002

1. Цель работы

1.1. Ознакомление с методикой тестирования каналов связи телекоммуникационных систем с помощью BER-тестера (Bit-Error-Rate – интенсивность поступления ошибочных битов от объекта проверки; определение дано в международном стандарте ITU-T O.153).

1.2. Разработка логической модели BER-тестера и анализ ее поведения в отсутствие и при наличии моделируемых ошибок в канале связи.

2. Основные сведения о BER-тестерах

2.1. Генераторы псевдослучайных битовых последовательностей

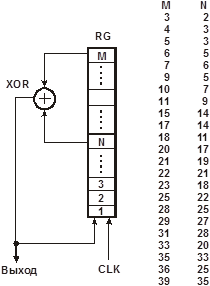

При тестировании каналов связи обычно применяют генераторы псевдослучайных битовых последовательностей. Пример схемы такого генератора приведен на рис. 2.1 [1]. Генератор выполнен на основе кольцевого сдвигового регистра RG с логическим элементом Исключающее ИЛИ (XOR) в цепи обратной связи. Если в исходном состоянии в регистре присутствует любой ненулевой код, то под действием синхросигнала CLK этот код будет непрерывно циркулировать в регистре и одновременно видоизменяться. В качестве выхода генератора можно также использовать выход любого разряда

При тестировании каналов связи обычно применяют генераторы псевдослучайных битовых последовательностей. Пример схемы такого генератора приведен на рис. 2.1 [1]. Генератор выполнен на основе кольцевого сдвигового регистра RG с логическим элементом Исключающее ИЛИ (XOR) в цепи обратной связи. Если в исходном состоянии в регистре присутствует любой ненулевой код, то под действием синхросигнала CLK этот код будет непрерывно циркулировать в регистре и одновременно видоизменяться. В качестве выхода генератора можно также использовать выход любого разряда

регистра.

Рис. 2.1. Обобщенная схема генератора псевдослучайной битовой

последовательности максимальной длины и таблица для выбора

промежуточной точки подключения обратной связи

В общем случае в М-разрядном регистре обратная связь подключается к разрядам с номерами М и N

(М > N). Приведенная на рис. 2.1 таблица описывает структуру генераторов различной разрядности. Каждый генератор формирует последовательность битов с максимальным периодом повторения, равным 2М – 1. В такой последовательности встречаются все М-разрядные коды, за исключением нулевого. Этот код представляет собой своеобразную “ловушку” для данной схемы: если бы нулевой код появился в регистре, дальнейшая последовательность битов была бы также нулевой. Но при нормальной работе генератора попадания в ловушку не происходит. Последовательность максимальной длины обладает следующими свойствами.

1. В полном цикле (2М – 1 тактов) число лог. 1 на единицу больше, чем число лог. 0. Добавочная лог. 1 появляется за счет исключения состояния, при котором в регистре присутствовал бы нулевой код. Это можно интерпретировать так, что вероятности появления на выходе регистра лог. 0 и лог. 1 практически одинаковы.

2. В полном цикле (2М – 1 тактов) половина серий из последовательных лог. 1 имеет длину 1, одна четвертая серий – длину 2, одна восьмая – длину 3 и т. д.

Такими же свойствами обладают и серии из лог. 0 с учетом пропущенного лог. 0. Это говорит о том, что вероятности появления “орлов” и “решек” не зависят от исходов предыдущих “подбрасываний”. Поэтому вероятность того, что серия из последовательных лог. 1 или лог. 0 закончится при следующем подбрасывании, равна 1/2 вопреки обывательскому пониманию “закона о среднем”.

3. Если последовательность полного цикла (2М – 1 тактов) сравнивать с этой же последовательностью, но циклически сдвинутой на любое число тактов W (W не является нулем или числом, кратным 2М – 1), то число несовпадений будет на единицу больше, чем число совпадений.

Идею тестирования канала связи с помощью прогона через него псевдослучайных битовых последовательностей удобно рассмотреть на примере использования пары устройств – скремблера и дескремблера.

2.2. Скремблер – дескремблер с неизолированными генераторами

псевдослучайных битовых последовательностей

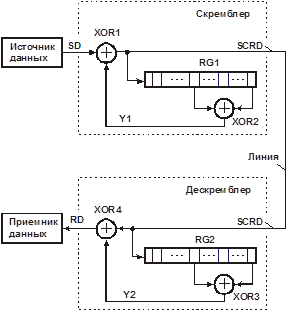

Скремблер (шифратор) и дескремблер (дешифратор) подключаются к противоположным сторонам канала связи, как показано на рис. 2.2. Скремблер и дескремблер выполнены на основе рассмотренных генераторов псевдослучайных битовых последовательностей. Оба генератора имеют одинаковую разрядность и однотипную структуру обратных связей. Все процессы, протекающие в системе передачи данных, синхронизируются от тактового генератора (на рисунке не показан). Этот генератор размещен на передающей стороне системы и может принадлежать источнику данных либо скремблеру. В каждом такте на вход скремблера подается очередной бит передаваемых данных SD, а в сдвиговом регистре RG1 накопленный код продвигается вправо на один разряд.

Рис. 2.2. Система передачи данных, в которой скремблер и дескремблер содержат неизолированные

генераторы псевдослучайных битовых последовательностей

Если предположить, что источник данных посылает в скремблер длинную последовательность лог. 0, то элемент XOR1 можно рассматривать как повторитель сигнала Y1 с выхода элемента XOR2. В этой ситуации регистр RG1 замкнут в кольцо и генерирует точно такую же псевдослучайную последовательность битов, как и в рассмотренной ранее схеме (см. рис. 2.1). Если от источника данных поступает произвольная битовая последовательность, то она взаимодействует с последовательностью битов с выхода элемента XOR2. В результате формируется новая (скремблированная) последовательность битов SCRD, по структуре близкая случайной. Эта последовательность, в свою очередь, продвигается по регистру RG1, формирует поток битов на выходе элемента XOR2 и т. д.

Скремблированная последовательность битов SCRD передается по линии (каналу связи) и поступает в дескремблер. С помощью генератора с фазовой автоподстройкой частоты (этот генератор на рисунке не показан) из входного сигнала выделяется тактовый сигнал. Под управлением тактового сигнала биты SCRD продвигаются в регистре RG2, а в приемник данных поступают дескремблированные данные RD.

Потоки данных RD и SD совпадают с точностью до задержки передачи по линии. Действительно, в установившемся режиме в сдвиговых регистрах RG1 и RG2 присутствуют одинаковые коды, так как на входы этих регистров поданы одни и те же данные SCRD, а тактовая частота, по сути, общая. Поэтому Y2 = Y1, и, с учетом этого,

RD = SCRD Å Y2 = SD Å Y1 Å Y2 = SD Å Y1 Å Y1 = SD Å 0 = SD.

Рассмотренная система передачи данных не требует применения какой-либо специальной процедуры начальной синхронизации. После заполнения сдвигового регистра RG2, как было показано, генераторы псевдослучайных битовых последовательностей работают синхронно (их состояния всегда одинаковы). При появлении одиночной ошибки в линии синхронизация временно нарушается, но затем автоматически восстанавливается, как только правильные данные вновь заполнят регистр RG2. Однако в процессе продвижения ошибочного бита по сдвиговому регистру RG2, а именно, в периоды его попадания сначала на первый, а затем на второй вход элемента XOR3 сигнал Y2 дважды принимает неправильное значение. Это приводит к размножению одиночной ошибки – она впервые появляется в сигнале RD в момент поступления из линии и затем возникает еще два раза при последующем двукратном искажении сигнала Y.

При тестировании линии источник данных выдает постоянный нулевой сигнал

SD = 0. Скремблер генерирует псевдослучайную последовательность битов. Дескремблер восстанавливает прообраз принятого псевдослучайного сигнала. При отсутствии ошибок передачи в приемник данных поступает постоянный нулевой сигнал RD = 0. Обнаружение пачки из трех импульсов (из-за размножения ошибки в регистре RG2) расценивается приемником данных как одиночная ошибка передачи данных по линии связи.

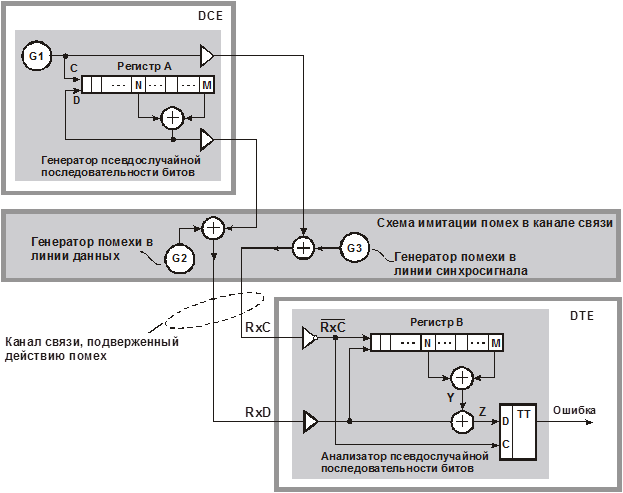

2.3. Вариант практической реализации тестера – объект моделирования

Как показано на рис. 2.3, для тестирования цепей передачи синхросигналов RxC и данных RхD канала связи между устройствами DTE и DCE использованы генератор и анализатор псевдослучайных последовательностей битов. По существу, генератор и анализатор представляют собой рассмотренные ранее скремблер и дескремблер, причем скремблируется сигнал “Постоянный нуль”, т. е. последовательность нулевых битов

(SD = 0, см. рис. 2.2). В отсутствие ошибок передачи сигналов RxC и RxD сигнал на выходе триггера TT также должен быть нулевым.

Для имитации помех в канале связи использованы генераторы G2 и G3. Генератор G2 в определенном такте (тактах) формирует сигнал лог. 1. Этот сигнал воздействует на логический элемент Исключающее ИЛИ, в результате элемент временно переводится в режим инвертирования передаваемого через него бита (битов) данных. Таким образом, вместо истинного нулевого бита передается ложный единичный или наоборот. Для имитации канала связи без помех в линии передачи данных на выходе генератора G2 должен постоянно присутствовать сигнал лог. 0.

Аналогично имитируется сигнал помехи, действующей на линию передачи синхросигнала. В отсутствие помех на выходе генератора G3 постоянно присутствует сигнал лог. 0. Появление в некотором такте на выходе генератора G3 сигнала лог. 1 приводит к временному искажению синхросетки передаваемых данных, так как при этом теряется один синхроимпульс.

Рис. 2.3. Система контроля передачи данных и синхросигнала между устройствами типа DCE и DTE

В отсутствие ошибок под управлением сигнала RxC с генератора G1 в линию данных RxD из регистра А поступает псевдослучайная последовательность битов (см.

рис. 2.4). Положительные фронты сигнала RxC задают границы битовых интервалов сигнала RxD. Положительные фронты инвертированного сигнала RxC задают смещенную на половину такта синхросетку приема данных в регистр В и в D-триггер ТТ. Такты работы генератора псевдослучайной последовательности битов обозначены символами Т1 с соответствующими индексами в скобках (например Т1(L + 4)). Аналогично такты работы анализатора обозначены символами Т2.

В тактах T1(J) … T1(J + 3) состояние регистра А изменяется в такой последовательности: S(J), S(J + 1), S(J + 2), S(J + 3). Соответствующие биты выходных данных: D(J), D(J + 1), D(J + 2), D(J + 3). Как отмечалось при описании системы “скремблер – дескремблер”, в установившемся режиме при отсутствии ошибок содержимое передающего и приемного регистров (в данном случае, регистров А и В) одинаково. Поэтому, как показано на временных диаграммах, коды в регистре В совпадают с кодами в регистре А с учетом взаимного смещения синхросеток на половину такта.

| Рис. 2.4. Временные диаграммы передачи и приема тестовых битовых последовательностей |

Интересно отметить, что код в приемном регистре (В) формируется на половину такта раньше, чем тот же код в передающем регистре (А)! Такое поведение анализатора можно рассматривать как предсказание очередного правильного бита (0 или 1) в ожидании его поступления по линии RxD. Как следует из временных диаграмм, в отсутствие ошибок предсказания полностью оправдываются. Это проявляется в том, что сигнал Z на входе данных D-триггера принимает устойчивое нулевое значение в моменты записи, поэтому триггер остается в состоянии лог. 0.

Предположим, что в такте Т1(J + 4) в результате воздействия на линию RxD импульса помехи передаваемый бит исказился: вместо истинного лог. 0 передается ложная лог. 1 или наоборот. В этой ситуации во второй половине такта Т2(J + 4) обнаруживается несоответствие предсказанного и фактически принятого битов (сигнал Z принимает стабильное значение, равное лог. 1). Поэтому в следующем такте Т2(J + 5) триггер переходит в состояние лог. 1. Таким образом, первое проявление ошибки зафиксировано с задержкой в половину такта после ее возникновения в линии.

Начиная с такта Т1(J + 5) по линии RxD вновь передаются правильные биты. Сравнение предсказанных и фактически принятых битов вновь дают положительные результаты, но ранее принятый в регистр В ошибочный бит начинает продвижение к разряду N. Код в регистре В искажен (что отражено на диаграмме символами “ERR”), но искажения пока внешне не проявляются.

В такте Т2(К + 2) ошибочный бит попадает в разряд N. Вследствие этого происходит неправильное предсказание ожидаемого бита, т. е. во второй половине такта предсказанный бит Y противоположен правильному биту D(K + 2), полученному по линии RxD. Поэтому триггер повторно регистрирует ошибку. После этого ошибочный бит продолжает продвижение по регистру В в направлении разряда М. В такте T2(L + 1) ошибочный бит достигает разряда М. Неправильное предсказание повторяется, триггер в третий раз регистрирует ошибку. После этого ошибочный бит выталкивается из сдвигового регистра В и, следовательно, более не влияет на работу системы контроля. Таким образом, одиночная ошибка в линии приводит к формированию пачки из трех импульсов на выходе триггера.

3. Формулировка задания

--> ЧИТАТЬ ПОЛНОСТЬЮ <--