Курсовая работа: Разработка схемы блока арифметико-логического устройства для умножения двух двоичных чисел

![]() (3.6)

(3.6)

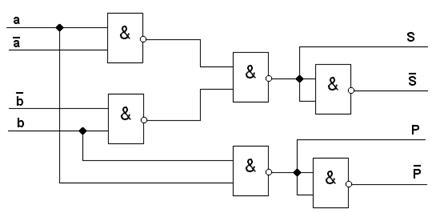

По полученным выражениям строим принципиальную схему (рис.3.3).

Рисунок 3.3 Принципиальная схема полусумматора.

Потребляемую схемой мощность найдем по формуле:

![]() . (3.7)

. (3.7)

где N – количество логических элементов в схеме;

![]() – мощность, потребляемая одним элементом.

– мощность, потребляемая одним элементом.

Количество элементов в схеме равно 83 а мощность элемента – ![]() . Подставляя данные в формулу (3.7) получим:

. Подставляя данные в формулу (3.7) получим:

![]() .

.

Время вычисления будет максимально в случае формирования переноса последовательно в семи младших разрядах сумматора. Таким образом, время счета будет определяться как сумма времени формирования переноса в семи младших разрядах и времени формирования выходного сигнала в старшем разряде:

![]() , (3.8)

, (3.8)

где ![]() – время срабатывания одного логического элемента;

– время срабатывания одного логического элемента;

![]() – максимальный путь (количество последовательно пройденных элементов) формирования переноса в i-ом разряде;

– максимальный путь (количество последовательно пройденных элементов) формирования переноса в i-ом разряде;

![]() – максимальный путь формирования результата в старшем разряде (3 элемента).

– максимальный путь формирования результата в старшем разряде (3 элемента).

Время срабатывания равно 4![]() . Пути

. Пути ![]() для сумматора (разряды 1 – 7) и для полусумматора (разряд 0) равны трём. Тогда по формуле (3.8) получим:

для сумматора (разряды 1 – 7) и для полусумматора (разряд 0) равны трём. Тогда по формуле (3.8) получим:

![]() .

.

3.2 Синтез регистров

Для хранения и сдвига множителя Y и суммы S необходим шестнадцатиразрядный регистр сдвига. Для хранения множимого понадобится один восьмиразрядный регистр RgX.

Структурная схема регистра сдвига показана на рис.3.4, из которого видно, что необходимо синтезировать одну комбинационную схему. Таблица истинности для этой схемы представлена в табл. 3.3, где значение управляющего сигнала W/Sравное нулю соответствует режиму записи, а равное единице - режиму сдвига на один бит вправо за такт.

Рисунок 3.4 Структурная схема регистра сдвига.

Таблица 3.3

| D | Q | S | J |

| X | 0 | 0 | 0 |

| X | 1 | 0 | 1 |

| 0 | X | 1 | 0 |

| 1 | X | 1 | 1 |

По приведенной таблице истинности находим логические выражения, описывающие работу синтезируемой схемы, и приводим их к заданному базису.

![]() (3.9)

(3.9)

Рисунок 3.5 Схема управления сдвигом.

Принципиальная схема, построенная по выражению (3.9), приведена на рис.3.5.

Восьмиразрядный регистр для хранения Х будет представлять собой восемь JK – триггеров с объединенными тактовыми входами.