Курсовая работа: Разработка схемы блока арифметико-логического устройства для умножения двух двоичных чисел

ВВЕДЕНИЕ

Арифметико-логические устройства (АЛУ) служат для выполнения арифметических и логических преобразований над словами, называемыми в этом случае операндами. Операндами могут быть двоичные числа с фиксированной запятой (дробные и целые), двоичные (или шестнадцатеричные) числа с плавающей запятой, десятичные целые числа, команды или отдельные их поля, логические коды, алфавитно-цифровые поля. Операнды могут иметь постоянную или переменную длину.

Выполняемые в АЛУ операции можно разделить на группы:

- операции двоичной арифметики для чисел с фиксированной запятой;

- операции двоичной арифметики для чисел с плавающей запятой;

- операции десятичной арифметики;

- операции индексной арифметики;

- операции специальной арифметики;

- операции над логическими кодами (логические операции);

- операции над алфавитно-цифровыми полями.

К арифметическим операциям относятся сложение, вычитание, умножение и деление. Группу логических операций составляют операции дизъюнкции (логическое ИЛИ) и конъюнкции (логическое И). Специальные арифметические команды включают нормализацию, арифметический сдвиг, логический сдвиг.

Можно привести следующую классификацию АЛУ.

По способу действия над операндами АЛУ делятся на последовательные и параллельные. В последовательных АЛУ операнды представляются в последовательном коде, а операции производятся последовательно во времени над их отдельными разрядами. В параллельных АЛУ операнды представляются параллельным кодом и операции совершаются параллельно во времени над всеми разрядами операндов.

По способу представления чисел различают АЛУ:

- для чисел с фиксированной запятой;

- для чисел с плавающей запятой;

- для десятичных чисел.

АЛУ для чисел с фиксированной запятой в свою очередь делятся на АЛУ с дробными и АЛУ с целыми числами.

По способу реализации работы различают асинхронные и синхронные АЛУ. В асинхронных АЛУ определяется момент фактического окончания операции, после чего немедленно может начинаться следующая операция. В синхронных АЛУ независимо от фактической продолжительности операции, определяющейся значениями операндов, на выполнение отдельных операций отводится фиксированное время.

По характеру использования элементов и узлов АЛУ делятся на блочные и многофункциональные. В блочном АЛУ операции над числами с фиксированной и плавающей запятой, десятичными числами и алфавитно-цифровыми полями выполняются в отдельных блоках. При этом повышается скорость работы, т.к. блоки могут параллельно выполнять соответствующие операции, но при этом значительно возрастают затраты на оборудование. В многофункциональных АЛУ операции для всех форм представления чисел выполняются одними и теми же схемами, которые коммутируются нужным образом в зависимости от требуемого режима работы.

По своим функциям АЛУ является операционным блоком, выполняющим микрооперации, обеспечивающие прием из других устройств (например, памяти) операндов, их преобразование и выдачу результатов в другие устройства. АЛУ управляется управляющим блоком, генерирующим управляющие сигналы, инициирующие выполнение в АЛУ определенных микроопераций. Генерируемая управляющим блоком последовательность сигналов определяется кодом операции команды и оповещающими сигналами.

Проектирование АЛУ включает выбор кодов для представления данных, определение алгоритмов выполнения отдельных операций, структур операционных блоков и реализуемых в них наборов микроопераций. Затем производят объединение отдельных операционных блоков и соответствующих наборов микроопераций в один многофункциональный операционный блок или несколько блоков для отдельных групп операций. Стремление обеспечить возможность эффективного объединения операционных блоков отдельных операций влияет на выбор их структур.

1. Описание алгоритма вычисления

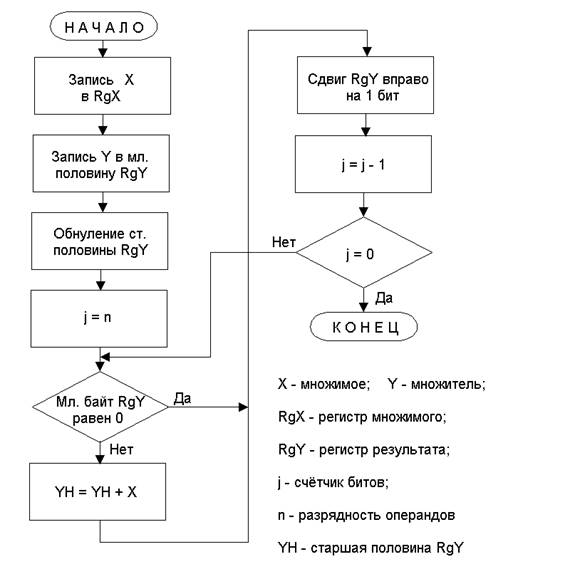

Заданный алгоритм целочисленного умножения двоичных чисел, начиная с младших разрядов, при неподвижном множимом и сдвиге суммы частичных произведений вправо, представлен на рис.1. В начале происходит проверка младшего разряда множителя Y, если он равен 1, то к старшей половине RgY прибавляется множитель X, а затем происходит сдвиг содержимого регистра RgY вправо на один разряд.

Рисунок 1 Алгоритм умножения с неподвижным множимым и сдвигом суммы частичных произведений вправо.

Рисунок 1 Алгоритм умножения с неподвижным множимым и сдвигом суммы частичных произведений вправо.

При нулевом младшем разряде суммирование не производится, а происходит лишь сдвиг. Далее счетчик разрядов уменьшается на единицу. Описанная последовательность действий повторяется до тех пор, пока счетчик разрядов не станет равным нулю. После этого переменная Z (сумма частичных произведений) становится результатом вычисления - произведением.

Для восьмиразрядного множимого и восьмиразрядного множителя процесс умножения будет выглядеть следующим образом :

Пусть X = 10011101, Y = 00111001, X´Y = Z

| N такта | Y H | Y L | J |

| 1 | 0 0 0 0 0 0 0 0 | 0 0 1 1 1 0 0 1 | 0 |

| 2 | 1 0 0 1 1 1 0 1 | 0 0 1 1 1 0 0 1 | 0 |

| 3 | 0 1 0 0 1 1 1 0 | 1 0 0 1 1 1 0 0 | 1 |

| 4 | 0 1 0 0 1 1 1 0 | 1 0 0 1 1 1 0 0 | 1 |

| 5 | 0 0 1 0 0 1 1 1 | 0 1 0 0 1 1 1 0 | 2 |

| 6 | 0 0 1 0 0 1 1 1 | 0 1 0 0 1 1 1 0 | 2 |

| 7 | 0 0 0 1 0 0 1 1 | 1 0 1 0 0 1 1 1 | 3 |

| 8 | 1 0 1 1 0 0 0 0 | 1 0 1 0 0 1 1 1 | 3 |

| 9 | 0 1 0 1 1 0 0 0 | 0 1 0 1 0 0 1 1 | 4 |

| 10 | 1 1 1 1 0 1 0 1 | 0 1 0 1 0 0 1 1 | 4 |

| 11 | 0 1 1 1 1 0 1 0 | 1 0 1 0 1 0 0 1 | 5 |

| 12 | 0 0 0 1 0 1 1 1 | 1 0 1 0 1 0 0 1 | 5 |

| 13 | 1 0 0 0 1 0 1 1 | 1 1 0 1 0 1 0 0 | 6 |

| 14 | 1 0 0 0 1 0 1 1 | 1 1 0 1 0 1 0 0 | 6 |

| 15 | 0 1 0 0 0 1 0 1 | 1 1 1 0 1 0 1 0 | 7 |

| 16 | 0 1 0 0 0 1 0 1 | 1 1 1 0 1 0 1 0 | 7 |

| 17 | 0 0 1 0 0 0 1 0 | 1 1 1 1 0 1 0 1 | 0 |

| 18 | 0 0 1 0 0 0 1 0 | 1 1 1 1 0 1 0 1 | 0 |

Результат произведения Z = 0010001011110101 . Полученный результат нетрудно проверить. В десятичной системе будем иметь Х = 157, Y = 57. Тогда результат в десятичной системе будет равен Z = 8949. Таким образом, чтобы умножить два восьмиразрядных числа, необходимо произвести восемь раз сложение и восемь раз сдвиг.

--> ЧИТАТЬ ПОЛНОСТЬЮ <--