Реферат: Описание процессоров семейства ADSP

ADSP-2181 два DMAпорта внутренний (IDMA) порт и байтовый (BDMA). IDMAпорт обеспечивает эффективную связь между главной системой и сигнальным процессором. Он используется для связи с внутренней памятью программы и памятью данных за один такт процессора. IDMA порт имеет 16-разрядный мультиплексный адрес и шину данных. IDMA порт полностью ассинхронный и может работать даже когда процессор полностью занят.

Байт памяти контроллера DMA позволяет загружать и сохранять комманды программ и данные, находящиеся в памяти. BDMAсхема способна обращаться к ячейке памяти, в то время как процессор работает в обычном режиме, используя только один такт процессора для передачи 8-,16- или 24-разрядных данных.

4.5. Аналоговый интерфейс

Входной аналоговый интерфейс состоит из входных усилителей и 16-разрядного аналогоцифрового преобразователя (ADC). Аналогично на выходе находится цифроаналоговый преобразователь и выходной дифференциальный усилитель.

5. ADSP-2100 - средства разработки

Семейство ADSP-2100 сопровождается полным набором программного обеспечения и аппартных средств для разработки. Система средств разработки для ADSP-2100 включает утилиты программного обеспечения для разработки программы и EZ-комплект для отладки аппаратных средств.

Программное обеспечение включает:

· SystemBuilder(системный составитель программы) – определяет структуру аппаратной системы. Он описывает количество внешней памяти и доступные порты ввода/вывода.

· Assembler (ассемблер) – транслирует исходный код и модули данных и обеспечивает синтаксис высокого уровня. В дополнение к полной диагностике системы Ассемблер обеспечивает макро обработку: включение файлов и модульную обработку кода.

· Linker (компановщик) – связывает раздельные модули программы, получая связанный код, и направляет его к аппаратным средствам, описанным с помощью System Builder.

· Simulator (тренажер) – выполняет интерактивное моделирование аппаратной конфигурации описанной SystemBuilder. Он отмечает запрещенные команды и поддерживает полную символическую трансляцию и дизассемблирование.

· PROMSplitter – этот модуль по выходным данным компановщика генерирует код совместимый с форматом памяти PROM.

· Ccompiler (С транслятор) – читает исходники написаные на С в формате ANSI и код на языке семейства ADSP-2100, готовый к ассемблированию.

Вычислительные модули

1. Краткое описание

1.1. Двоичные строки

Двоичные строки - самое простое представление чисел в процессорах семейства ADSP-2100. Этот формат, например, используют элементарные логические функции: NOT, OR, AND, XORи т.д. Вычислительный модуль ALU обрабатывает эти числа ввиде двоичных последовательностей не привлекая возможности работы с плавающей точкой и знаковым разрядом.

1.2. Беззнаковые числа

Под двоичными числами без знака понимаются положительные числа. Диапазон их представления в процессоре в два раза больше чем у чисел со знаком. Числа большой точности обрабатываются как беззнаковые.

1.3. Числа со знаком: двойное дополнение

Расматривая арифметику семейства ADSP-2100 знаковые числа можно отнести к числам с двойным дополнением. Дольшенства операций процессора поддерживают работу с двойным дополнением. Процессоры семейства ADSP-2100 не поддерживают работу с остатками и BCD-форматом.

1.4. Дробное представление: 1.15

Арифметики ADSP-2100 приспособленна для работы с числами в дробном двочном формате, называемом 1.15. В этом формате имеется один знаковый разряд (MSB) и пятнадцать дробных битов.

Далее представленны весовые значения битов в формате 1.15:

–20 2 –1 2 –2 2 –3 2 –4 2 –5 2 –6 2 –7 2 –8 2 –9 2 –10 2 –11 2 –12 2 –13 2 –14 2 –15

| Числа в формате 1.15 | Десятичный эквивалент |

0x0001 0x7FFF 0xFFFF 0x8000 | 0.000031 0.999969 –0.000031 –1.000000 |

1.5. Арифметика ALU

Все комманды ALU обрабатывают операнды, как двоичные 16-разрядные последовательности. Биты состояния: AV- переполнение, AN – знак.

Логика бита переполнения основана на арифметике двойного дополнения. Например при сложении двух положительных чисел получается положительный результат, но может повлечь за собой переполнение. При сложении двух чисел с разными знаками результат может быть как положительным так и отрицательным, но переполнение в этом случае невозможно.

Логика бита переноса основана на арифметике чисел без знака. Он устанавливается если перенос сгенерирован 16-ым битом (MSB).

1.6. Арифметика MAC

Операциив модуле MAC производятся над числами, представленными ввиде двоиных последовательностей и результет выдается в том же виде.

Процессоры семейства ADSP-2100 поддерживают два режима корректировки формата: дробный режим – для дробных операндов (формат 1.15) и целочисленный режим для целых чисел формата 16.0.

Когда процессор умножает два операнда в формате 1.15 в результате получается число 2.30 (два знаковых и 30 дробных разряда). В дробном режиме МАС автоматически сдвигает результат на один бит влево перед пересылкой его в регистр результата (MR). Этим сдвигом результат приводится к виду 1.31, который может быть округлед до формата 1.15.

В целочисленном режиме сдвига влево не происходит. Напрмер при умножении операндов 16.0 результат представляется ввиде 32.0. Сдвиг влево в этом случае не нужен, т.к. он изменит числовое представление результата.

1.7. Резюме

Таблица 1.1 обобщает некоторые арифметические характеристики процессоров семейства ADSP-2100.

Таблица 1.1

| Операции | Арифметические форматы | |

| Операнды | Результат | |

| ALU | ||

| Сложение | Знаковые или без знака | Установка флагов |

| Вычитание | Знаковые или без знака | Установка флагов |

| Логические операции | Двоичные строки | Тот же, что и операнды |

| Деление | Явно знаковые/без знака | Тот же, что и операнды |

| Переполнение ALU | Знаковые | Тот же, что и операнды |

| Бит коррекции ALU | 16-разрядные без знака | Тот же, что и операнды |

| Насыщение ALU | Знаковые | Тот же, что и операнды |

| MAC (дроб.) | ||

| Умножение (Р) | 1.15 Явно знаковые/без знака | 32 разряда (2.30) |

| Умножение (MR) | 1.15 Явно знаковые/без знака | 2.30 сдвинутый к 1.31 |

| Умножение с накоплением | 1.15 Явно знаковые/без знака | 2.30 сдвинутый к 1.31 |

| Умножение с вычитанием | 1.15 Явно знаковые/без знака | 2.30 сдвинутый к 1.31 |

| Насыщение МАС | Знаковые | Тот же, что и операнды |

| МАС(цел.) | ||

| Умножение (Р) | 1.15 Явно знаковые/без знака | 32 разряда (2.30) |

| Умножение (MR) | 16.0 Явно знаковые/без знака | 32.0 без сдвига |

| Умножение с накоплением | 16.0 Явно знаковые/без знака | 32.0 без сдвига |

| Умножение с вычитанием | 16.0 Явно знаковые/без знака | 32.0 без сдвига |

| Насыщение МАС | Знаковые | Тот же, что и операнды |

| Shifter | ||

| Логические сдвиги | Баз знака/двоичные строки | Тот же, что и операнды |

| Арифметические сдвиги | Знаковые | Тот же, что и операнды |

| Определение порядка | Знаковые | Тот же, что и операнды |

2. Арифметико-логический модуль ALU

Модуль ALU предоставляет набор стандартных арифметических и логических функций. Арифметические функции: сложение, вычитание, отрицание, инкремент, декремент и модуль.Они дополненны двумя примитивами деления, с помощью которых возможна реализация цикла многократного деления. Логические: OR, AND, XOR (исключающее ИЛИ) и NOT.

2.1. Блок-схема ALU

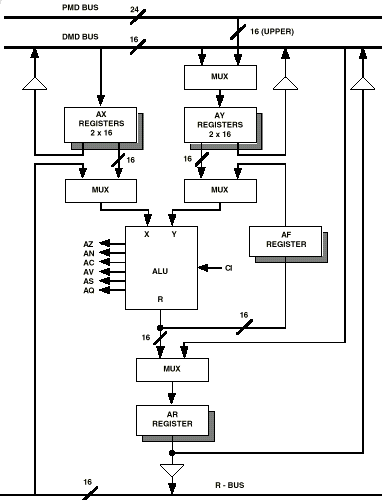

На рисунке 2.1 показана структурная схема вычислительного модуля ALU.

|

ALU – это 16-разрядное устройство с двумя 16-разрядными портами ввода данных Xи Y,и одним портом вывода - R . ALU генерирует шесть сигналов состояния: ноль (AZ), негатив (AN), перенос (AC), переполнение (AV), знак (AS) и quotient (AQ). В конце каждого цикла эти сигналы сохраняются в регистре состояния процессора (ASTAT).