Реферат: Описание процессоров семейства ADSP

· AN – NEGATIV - знаковый разряд результата ALU. Единица, если результат отрицательный.

· AV – OVERFLOW – устанавливается в единицу, если происходит переполнение ALU.

· AC – CARRY – бит переноса.

· AS – SIGN – знаковый разряд входного X-порта ALU. Необходим только для команды ABS.

· AQ – QUOTIENT – бит частного. Генерируется только командами DIVSи DIVQ.

3. Вычислительный модуль умножения с накоплением (MAC)

Вычислительный модуль МАС обеспечивает быстрое умножение, умножение с добавлением, умножение с вычитанием, функции насыщения и очистка в ноль. Функция обратной связи позволяет части результата в одном цикле быть одним из сомножителей в следующем.

3.1. Описание блок-схемы МАС

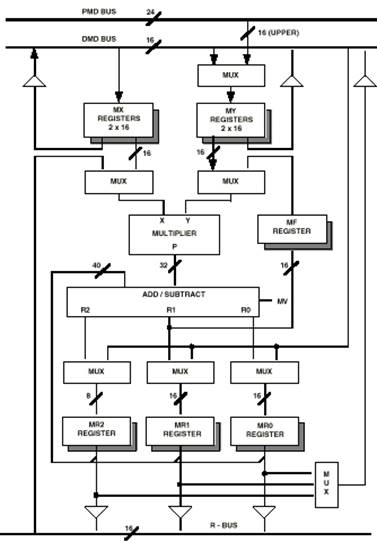

На рисунке 3.1. показана блок-схема вычислительного модуля умножения с накоплением.

МАС имеет два входных 16-разрядных порта X и Y и 32-разрядный порт вывода результата P. 32-разрядный результат поступает в 40-разрядный блок сложения/вычитания, который либо прибавляет, либо вычитает текущий результат из регистра результата МАС (MR), либо передает текущий результат непосредственно в MR (регистр MR имеет 40 разрядов). Фактически регистр MR состоит из трех (MR0 и MR1 – 16-разрядные и MR2 – 8-рахрядный) регистров.

|

Блок сложения/вычитания имеет более 32 разрядов затем, чтобы учесть промежуточные переполнения в ряде операции умножения с накоплением. Бит признака МV (переполнение) устанавливается в единицу, если значение аккумулятора превышает 32 разряда, т.е. в старшей части регистра результата MR есть девять значащих битов (без знака).

Регистры ввода-вывода подобны регистрам ALU.

Порт Х может принимать данные из регистра MX или из любого другого регистра на R-шине (результата). R-шина соединяет выходные регистры всех вычислительных модулей, для непосредственного использования результатов вычислений в качестве входных операндов. Регистр MX состоит из двух: MX0 и MX1. Они читаются и записываются с DMD-шины. Выводы регистров MX0 и MX1 устроены таким образом, что один поставляет множитель в блок умножения, а другой управляет DMD-шиной.

Порт Y принимает данные из регистра MY или регистра обратной связи MF. MY так же разбит на два регистра (MY0 и MY1), доступ к которым осуществляется с DMD-шины и возможна запись в низ с PMD-шины. Система команд предусматривает чтение этих регистров с помощью PMD-шины, но прямого доступа для этой операции нет, в этом случае используется модуль DMD-PMD обмена. Выводы регистра MY устроены аналогично MX.

Результат умножения поступает либо в блок сложения/вычитания, либо в регистры MY или MF. Регистр обратной связи MFпозволяет 16-31-разрядному результату вычисления в предыдущем цикле становится операндом умножения на входе Y, в следующем. 40-разрядный регистр MR разделен на три секции (MR0, MR1, MR2). Содержимое любой из них может быть выведено на DMD- или R-шину и записано с DMD-шины.

Любой из регистров МАС может читаться и записываться в одном цикле (чтение в начале цикла, запись - в конце). Прочитанное содержимое регистра в начале одного цикла записано в конце предыдущего, следовательно новое значение регистра может быть прочитано только в течении следующего цикла. Это позволяет входному порту предоставлять операнд для МАС в начале цикла и оперировать со следующим значением из памяти в конце того же цикла. Это относится и к выходному регистру.

Регистры MR, MF, MX, MYпродублированы во вторичном банке (на рис.3.1. он показан на заднем плане). Одновременно доступен лишь один из банков. Дополнительный банк регистраторов может быть активизирован для чрезвычайно быстрого контекстного переключения. Таким образом новая задача, типа подпрограммы обработки прерывания, может выполняться без сохранения текущих данных в памяти.

Выбор первичного или дополнительного банка регистров определяется установкой нулевого бита в регистре MSTAT состояний процессора. Если этот бит установлен в 0, то выбран первичный банк.

3.2. Операции МАС

В этом разделе описываются операции вычислительного модуля МАС, входные форматы данных, обработка переполнения и насыщения.

3.2.1. Стандартные функции

Набор стандартных операций перечислен в таблице 3.1.

Таблица 3.1

| Название | Назначение |

| X×Y | Умножение X на Y |

| MR+X×Y | Умножение и сложение с MR |

| MR-X×Y | Умножение и вычитание из MR |

| 0 | Очистка MR |

ADSP-2100 обеспечивают два режима работы операции умножения с накоплением: работы с дробными числами (1.15) и работа с целыми числами (16.0).

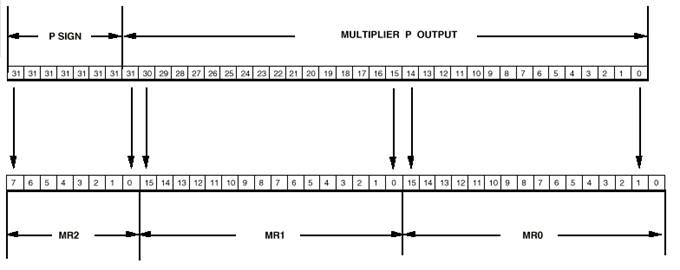

В дробном режиме выходной регистр P корректирует формат, т.е. прежде чем добавить значение в MR оно сдвигается на один разряд влево. Таким образом, бит 31 регистра P запишется в бит 32 регистра MR, а 0-ой бит – в первый. В позицию LSB, при этом записывается ноль. На рисунке 3.2. показан дробный формат работы модуля умножения.

|

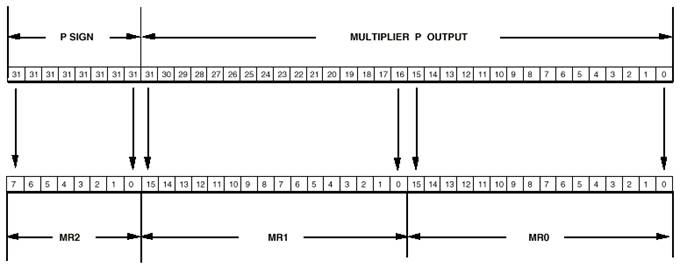

В целочисленном формате (рис.3.3) регистр P не сдвигается прежде чем прибавиться к MR.

|

Выбор режима осуществляется установкой 4 бита регистра MSTAT процессора. Если этот бит в 1, то выбран целочисленный режим. В любом формате блок умножения формирует 32-разрядный результат и передает его в блок сложения/вычитания, где получается конечное значение операции, которое записывается в MR.

3.2.2. Входные форматы

Для облегчения умножения входные операнды могут находится в любых форматах. Входные форматы определяются, как часть команды и выбираются динамически при обращению к блоку умножения.

1. Знаковый ´ знаковый – используется при умножении двух знаковых чисел простой точности или двух старших частей знаковых чисел двойной точности.

2. Без знака ´ знаковый (знаковый ´ без знака) - используется при умножении верхней части знакового числа на нижнюю часть другого или для умножения знакового числа простой точности с числом той же точности без знака.

3. Без знака ´ без знака – используется при умножении чисел простой точности без знака, или нижних частей знаковых чисел двойной точности.

3.2.3. Регистры ввода вывода МАС

Регистры для входного порта X – MX0, MX1, AR, MR0, MR1, MR2, SR0, SR1.

Регистры для входного порта Y – MY0, MY1, MF.