Реферат: Описание процессоров семейства ADSP

Порт ввода Yтакже принимает данные из двух источников: из регистра AY и регистра обратной связи ALU – AF. Регистр AY привязан к порту Y и состои из двух регистров AY0 и AY1. Эти регистры даступны для чтения и записи с DMD-шины и перезаписываемы с PMD-шины. Система комманд позволяет читать регистры AY0 и AY1 с помощью PMD-шины, но то же с использованием DMD-PMD модуля. Выводы ругистров AY0 и AY1 реализованы аналогично регистрам AX0 и AX1.

Выход ALUподключен к выходному регистру результата AR и через регистр обратной связи AF на вход. AF– внутренний регистр ALU, который позволяет результату вычисления использоваться в качестве следующего операнда. Регистр AR имеет выход на DMD- и R-шины. В системе комманд предусмотрена возможность чтения регистра ARпосредством PMD-шины аналогично двум предыдущим случаям.

Любой из регистров ALUдоступен для записи и чтения в течении цикла процессора (для чтения в начале цикла, для чтения - в конце). Таким образом, новое значение, записанное в конце одного цикла, может быть прочитанно лишь в начале следующего. Это позволяет входным регистрам записать в ALU опренд в начале цикла и считать следующий в конце того же цикла. Это так же позволяет сохранить содержимое регистра результата в памяти и прооперировать со следующим результатом в одном цикле.

ALUимеет двойные банки регистров AX, AY, AFи AR (на рис.2.1 это показано тенями). Но в один момент времени доступен только один банк. Доплнительный банк может быть активизирован для чрезвычайно быстрого контекстного переключения. В этом случае новая задача, подобно подпрограмме обработке прерывания, может выполнияться без сохранения текущих данных в памяти.

Выбор главного или альтернативного банка регистров определяется битом 0 регистра режимоа процессора MSTAT. Если этот бит – 0, то выбран главный банк, если – 1, то дополнительный.

2.2. Стандартные функции

Стандартные функции ALUперечисленны в таблице 2.1.

Таблица 2.1

| Функция | Назначение |

| R= X+Y | Сложение операндов Xи Y |

| R= X+Y+CI | Сложение операндов Xи Y и бита коррекции |

| R= X-Y | Вычитание операндов Xиз Y |

| R= X-Y+CI-1 | Вычитание операндов Xиз Y с заемом |

| R= -X | Инверсия X |

| R= -Y | Инверсия Y |

| R= X+1 | Инкремент X |

| R= Y+1 | Инкремент Y |

| R= X-1 | Декремент X |

| R= Y-1 | Декремент Y |

| R= PASS X | Операнд X не изменяет результата |

| R= PASS Y | Операнд Y не изменяет результата |

| R= 0 | Очистка результата |

| R= ABS X | Модуль X |

| R= X AND Y | Логическое умножение операндов Xи Y |

| R= X OR Y | Логическое сложение опреандов Xи Y |

| R= X XOR Y | Исключающее ИЛИ операндов Xи Y |

| R= NOT X | Отрицание X |

| R= NOT Y | Отрицение Y |

2.3. Регистры ввода вывода ALU

Регистры ввода ALUперечисленны ниже.

Регистры для порта X: AX0, AX1, AR, MR0, MR1, MR2, SR0, SR1.

Регистры для порта Y: AY0, AY1, AF.

Регистры для порта R: AR, AF.

Регистры MR0, MR1, MR2 являются регистрами результатов модуля MAC, а SR0, SR1 – модуля Shifter.

2.4. Возможность мультиточности

Операции мультиточности в ALU связаны с сигналом carry-in и битом переноса AC. Операция сложение с переносом предназначена для сложения старших частей мультиточных чисел, также как, вычитание с заемом – для их вычитания.

2.5. Режим насыщения ALU

Регистр AR имеет режим работы - насыщение, в котором он устанавливается в минимальное отрицательное значение или максимальное положительное, если операция заканчивается переполнением. Эта функция регистра AR становится возможной при установке 3 регистра MSTAT.

Таблица 2.2.

| Переполнение (AV) | Carry (AC) | Содержимое AR |

| 0 | 0 | Результат на выходе ALU |

| 0 | 1 | Результат на выходе ALU |

| 1 | 0 | 0111111111111111 (положит.) |

| 1 | 1 | 1000000000000000 (отриц.) |

2.6. Режим блокировки переполнения

Режим блокировки переполнения разрешается при установки бита 2 регистра MSTAT. В этом режиме при переполнении бит AV устанавливается и при последующих операциях остается в этом состоянии, таким образом следующее переполнение уже не генерируется. Бит состояния AV можно очистить непосредственно с DMD-шины.

2.7. Деление

ALU поддерживает методы деления. Деление осуществляется путем сложения и циклического сдвига с помощью двух специальных примитивов. Делить можно знаковые и без знаковые числа, однако делитель и делимое должны быть одного типа.

Обычная точность деления (32-разрядное делимое, 16-разрядный делитель, 16-разрядный остаток) реализуется за 16 циклов. Может быть получена большая или меньшая точность остатка. Делитель может быть сохранен в регистре AX0, AX1 или в любом регистре результатов R. Старший байт знакового делителя должен находиться либо в регистре AY1, либо в AF, без знакового – в AF. Младший байт делителя любого типа должен находиться в AY0. Остаток после деления будет записан в регистр AY0.

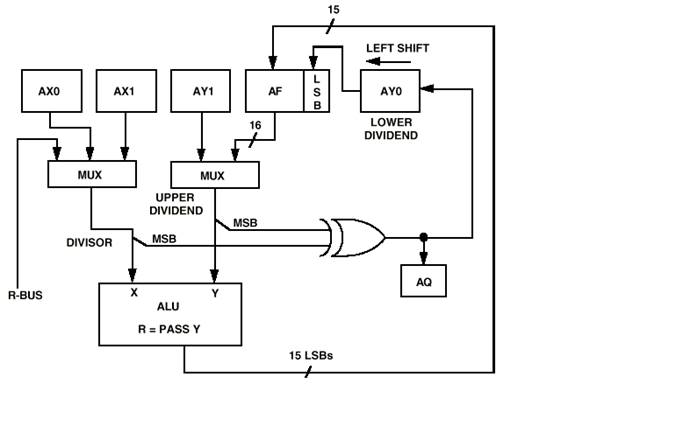

Первый из двух примитивов - это команда «деление-знак» (DIVS), преназначена для деления чисел со знаком. Она вычисляет знаковый бит остатка выполняя операцию исключающее-ИЛИ для знаковых разрядов делителя и делимого. Регистр AY0 сдвигается на одну позицию таким образом, чтобы знаковый разряд переместился в позицию LSB. Вычисленный зныковый разряд сохраняется в бит AQ регистра состояния. Структура операции DIVS показанна на рисунке 2.2.

При делении чисел без знака операция DIVS не применяется. В этом случае бит AQ устанавливается в 0 вручную. Он показывает, что остаток должен быть положительным.

|

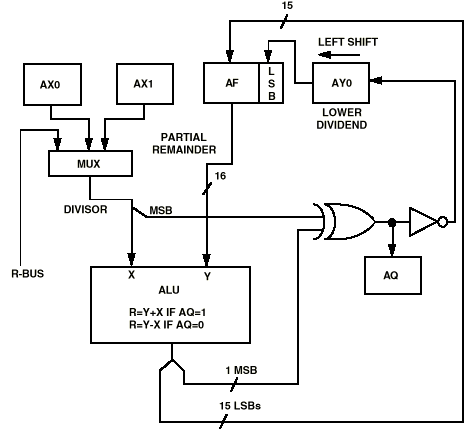

?????? ???????? ?? ??????? ??????? ? ??? ??????? DIVQ, ??????? ??????????? ???????????? ? ?????????? ?? ?????? ???? ????????. ??? ??????? ???????? ??????? ????? ??? ????? ??????? DIVQ??????????? 16 ???, ??? ????? ?? ???????? ??????? ????? ?? ?????? ???????? ??????????? 15 ??? ????? ?????????? ????????? ??????? ? ??????? ??????? DIVS. DIVQ ???????? ??????? AY0 ????? ?? ???? ?????? ???, ????? ????? ??? ???????? ???????? ? ??????? LSB. ????????? ???? AQ, ??????? ???????????? ?? ?????????? ????????, ?????????? ???????? ALU ??? ?????????? ?????????? ??????????. ???? AQ=1, ?? ALU ????????? ???????? ? ?????????? ?????????? ? AF. ???? AQ=0, ?? ALU ???????? ???????? ?? ?????????? ?????????? ? AF. ??? ?? ??? ? ? ???????? DIVSALU ??????? ????????? ? ??????? AF. ???????? DIVQ????????????????? ?? ???.2.3.

?????? ???????? ?? ??????? ??????? ? ??? ??????? DIVQ, ??????? ??????????? ???????????? ? ?????????? ?? ?????? ???? ????????. ??? ??????? ???????? ??????? ????? ??? ????? ??????? DIVQ??????????? 16 ???, ??? ????? ?? ???????? ??????? ????? ?? ?????? ???????? ??????????? 15 ??? ????? ?????????? ????????? ??????? ? ??????? ??????? DIVS. DIVQ ???????? ??????? AY0 ????? ?? ???? ?????? ???, ????? ????? ??? ???????? ???????? ? ??????? LSB. ????????? ???? AQ, ??????? ???????????? ?? ?????????? ????????, ?????????? ???????? ALU ??? ?????????? ?????????? ??????????. ???? AQ=1, ?? ALU ????????? ???????? ? ?????????? ?????????? ? AF. ???? AQ=0, ?? ALU ???????? ???????? ?? ?????????? ?????????? ? AF. ??? ?? ??? ? ? ???????? DIVSALU ??????? ????????? ? ??????? AF. ???????? DIVQ????????????????? ?? ???.2.3.

|

|

Иногда необходимо некоторое изменение формата делимого и делителя. Например, если оба операнда знаковые и дробные (делимое в формате 1.31, а делитель – 1.15), то результат запишется в формате 1.15, т.о. для правильного результата необходимо, чтобы делимое было меньше делителя.

Чтобы разделить два целых числа (делимое в формате 32.1, а делитель – 16), необходимо перед делением привести делимое к формату 31.1, т.е. сдвинуть его влево на один разряд.

Делимое: BBBBB.BBBBBBBBBBBBBBBBBBBBBBBBBBB

NL NR

Делитель: BB.BBBBBBBBBBBBBB

DL DR

Частное: BBBB.BBBBBBBBBBBB

(NL–DL+1) (NR–DR–1)

Алгоритм переполняется, если результат не представляется в формате частного, как вычислено выше и когда делитель равен нулю или меньше делимого.

2.8. Регистр состояния ALU

Назначение битов регистра ASTAT описано ниже: