Реферат: Разработка блока динамического ОЗУ с мультиплексором кода адреса

Мультиплексор DD9-DD12 выполненный на схемах К555КП2 обеспечивает последовательный во времени ввод адресного кода строк AX {AO-A7} и столбцов AY {A8-A15} в модуль ОЗУ.

Адресные сигналы поступают на входы D0.0, D1.0 и D0.1, D1.1 мультиплексорных микросхем и коммутируются на выхды под управлением сигнала на входе SED2(AY/AX) при наличии на другом управляющем входе SED1(REF) уровня 0. Условия коммутации сигналов: при AY/AX=0 к выходам подключаются каналы D0.0, D0.1 и, следовательно, на адресные входы ОЗУ поступает адрес строк AX; при AY/AX=1 к выходам подключаются каналы D1.0, D1.1 и к ОЗУ направляется код адреса столбцов AY.

Сигналы управления: REF- признак режима регенерации и AY/AX-сигнал мультиплексирования каналов, вырабатывает контроллер.

В режиме регенерации REF=1 и мультиплексор коммутирует на выходы при изменении AY/AX каналы D2.0, D3.0 и D2.1, D3.1. Но так как указанные каналы попарно соединены, то на результат коммутации сигнал AY/AX влияния не оказывает: при любых его значениях на выходы мультиплексора поступают адреса регенерации AR, вырабатываемые счетчиком контроллера. Эти сигналы адресуют только строки, сигналы адреса столбцов в этом режиме на адресных входах отсутствуют.

При отсутствии обращения к ОЗУ, ОЗУ работает только в режиме регенерации. С каждым тактом контроллер формирует сигналы RAS, REF и код адреса очередной строки, и инициирует работу модуля памяти по циклу регенерации.

Процесс регенерации прекращается при обращении микропроцессора к ОЗУ, и контроллер обрабатывает требование микропроцессора. В конце цикла обращения контроллер переводит блок ОЗУ в режим регенерации, продолжая этот процесс с адреса, на котором он был прерван.

Регенерация, осуществляемая по описанному алгоритму называется “ прозрачной”: она незаметна для микропроцессора и не снижает скорость обработки программ. Условием для применения этого способа является наличие временных интервалов между двумя любыми обращениями микропроцессора к ОЗУ, достаточных для проведения одного цикла регенерации, т.е. регенерации при обращении к модулю ОЗУ по одному адресу.

Например, алгоритмом работы микропроцессора К580ВМ80 такие интервалы предусмотрены: минимальный цикл между двумя любыми обращениями к памяти состоит из трех тактовых периодов.

При номинальной частоте генератора 18МГц длительность такта равна 0.5 мкс. Если учесть, что на выполнение одного цикла регенерации микросхем К565РУ3Г требуется 370 нс, то очевидна возможность реализации.

2.1.Принцип работы микросхемы динамических ОЗУ К565РУ3Г

В микросхемах памяти динамического типа функции ЭП выполняет электрический конденсатор, образованный внутри МДП структуры. Информация представляется в виде заряда: наличие заряда на конденсаторе соответствует логической 1, отсутствие-логическому 0. Поскольку время сохранения конденсатором заряда ограничено, предусматривают периодическое восстановление (регенерацию) записанной информации. Кроме того, для них необходима синхронизация, обеспечивающая требуемую последовательность включений и выключений функциональных узлов.

Для изготовления микросхем динамического ОЗУ в основном применяют n-МДП технологию, которая позволяет повышать быстродействие и уровень интеграции микросхем, обеспечивать малые токи утечки и за этот счет увеличивать время сохранения заряда на запоминающем конденсаторе.

- в![]()

![]()

![]()

![]()

![]() ыход на три состояния;

ыход на три состояния;

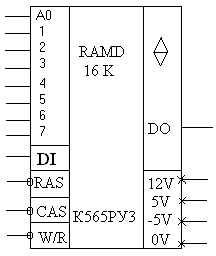

DI- входные данные; W/R- запись-считывание;

DO- выходные данные; A- адрес;

RAS- строб адреса строки;

CAS- строб адреса столбца;

Микросхема К565РУ3Г информационной емкостью 16Кx1бит. В ее структурную схему (приложение 1) входят выполненные в одном кремниевом кристалле матрица накопителя, содержащая 16384 элементов памяти, расположенных на пересечениях 128 строк и 128 столбцов, 128 усилителей считывания и регенерации, дешифраторы строк и столбцов, устройство управления, устройство ввода-вывода и мультиплексный регистр адреса.

Матрица накопителя разделена на две части по 64x64 ЭП в каждой. Между ними размещены усилители, так что каждый столбец состоит из двух секций, подключенных к разным плечам усилителя (приложение 2).

Элемент памяти собран по одно-транзисторной схеме и включает конденсатор Cij. Транзистор выполняет функции ключа: при сигнале на адресной шине строки Xi=1 он открывается и соединяет конденсатор Cij с j-разрядной шиной. Предварительно в паузах между обращениями к накопителю емкости полушин США и СШБ заряжает источник напряжения UO через открытые ключевые транзисторы VT5 и VT6. При обращении к накопителю эти транзисторы закрываются и изолируют полушины Aj и Bj от источника напряжения UО

Запоминающий конденсатор Сij выбранного ЭП подключается через открытый транзистор Vtij к полушине Aj и изменяет ее потенциал. Это изменение незначительнo, тк емкость запоминающего конденсатора равная 01-02 пФ много меньше емкости шины Поэтому для индикации малого изменения потенциала шины при считывании информации применен высоко чувствительный дифференциальный усилитель тригерного типа на транзисторах VT1-VT4 включенный в середину РШ

Кроме массива ЭП и усилителей матрица имеет в своей структуре опорные элементы (ЭО) по одному елементу в каждой полушине Эти элементы вкаждой половине матрицы состовляют опорную строку (ОС)

Опорный элемент построен аналогично запоминающему Его назначение состоит в поддержании опорного напряжения UO c которым усилитель сравнивает потенциал полушины с выбранным ЭП и реагирует на получающуюся при сравнении разность

потенциалов положительного и отрицательного знака в зависимости от считываемого уровня

Эта операция происходит следующем образом: если выбрана для обращения строка верхней полуматрицы Xi то сигнал А6 старшего разряда кода адреса строки коммутирует в селекторе опорной строки цепь через ключевой транзистор VT12 для сигнала F2 к ОС2 расположенной в нижней полуматрице Таким образом в каждом из 128 столбцов к усилителю с разных сторон подключены ЭП и ЭО Поскольку потенциал полушины с ЭП отличается от опорного в проводимости транзисторов разных плеч усилителя-триггера появляется асимметрия которая при включении цепи его питания сигналом F3 вызывает опрогидование триггера по преобладающему уровню В итоге на выходах-входах А и В триггера формируются полные уровни 1 и 0 Тот из сигналов который отражает считываемую информацию в данном примере сигнал с плеча А коммутируется на вход устройства вывода через ключевые транзисторы VT7VT9 и VT10 открываемые сигналами А6 F4 и Yj Очевидно считан может быть только один сигнал с выбранного дешифратором столбца : Yj=1 У остальных столбцов ключи VT10 закрыты Сигнал F4 зависит от наличия сигнала CAS: при отсутствии последнего он не формируется и ключ VT9 закрыт

Сигнал на входе-выходе А триггера-усилителя выполняет также функцию восстановления уровня заряда запоминающего конденсатора Cij , т.е. функцию регенерации информации. Причем эта операция происходит во всех ЭП выбранной строки одновременно.

Таким образом, при каждом обращении к матрице для считывания информации автоматически осуществляется регенерация информации во всех ЭП, принадлежащих выбранной строке.

Для адресации 16 К элементов памяти необходим 16-разрядный код, а у микросхемы только восемь адресных входов. С целью уменьшения числа необходимых выводов корпуса в микросхемах динамического ОЗУ код адреса вводят по частям: вначале семь младших разрядов АО-А7, сопровождая их стробирующим сигналом RAS, затем семь старших разрядов А8-А15 со стробирующим сигналом CAS. Внутри микросхемы коды адреса строк и столбцов