Учебное пособие: Типовые логические схемы последовательностного типа

Министерство образования Российской Федерации

Российский химико-технологический университет

им. Д.И. Менделеева

Новомосковский институт

Типовые логические схемыпоследовательностного типа

Методические указания

Под редакцией В.И. Воробьева

Новомосковск 2008

УДК 681.325

ББК 32.973

Т434

Рецензенты:

доцент кафедры "Автоматизация производственных процессов" В.И. Иванков, доцент кафедры "Автоматизация производственных процессов" В.Р. Предместин

Составитель Прохоров Виктор Сергеевич

Т434 Типовые логические схемы последовательностного типа.

Методические указания / НИ РХТУ им.Д.И. Менделеева. Сост.: В.С. Прохоров, под редакцией В.И. Воробьева, Новомосковск, 2008, 27 с.

Рассматривается работа, архитектурные и схемотехнические особенности типовых логических схем последовательностного типа, которые применяют в микропроцессорных системах.

Ил 43. Табл.5. Библиогр.7 назв.

УДК 681.322

ББК 32.973

© Российский химико-технологический университет им. Д.И. Менделеева, Новомосковский институт, 2008

Введение

В отличие от комбинационных схем (КС) значения выходных сигналов последовательностных схем (ПС) в данный момент времени зависят не только от значений входных сигналов в этот же момент времени, но и от их предыдущих значений. Из этого следует, что ПС реализует функциональную связь уже не между отдельными значениями входных и выходных сигналов, а между их последовательностями. Поэтому, в отличии от КС, работу ПС следует рассматривать во времени.

Для того, чтобы значения выходных сигналов зависели от предыдущих значений входных, ПС должны обладать памятью, в которой сохраняется информация о предыдущих входных воздействиях. Эта информация используется в ПС в виде совокупности сигналов, вырабатываемых памятью.

Особое значение при изучении последовательностных схем имеют элементы памяти – триггеры.

1. Триггеры

Триггеры – это логические устройства с памятью, которые способны длительно оставаться в одном из двух возможных устойчивых состояний и скачком чередовать их под действием внешних сигналов.

1.1 Триггерная ячейка

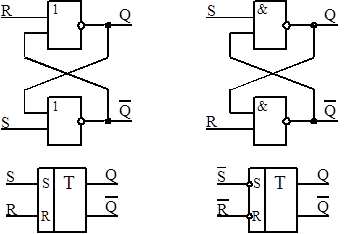

Основу триггеров составляют простейшие запоминающие ячейки, представляющие собой симметричную структуру из двух логических элементов ИЛИ-НЕ либо И-НЕ, охваченных перекрёстной обратной связью:

Рис.1.1 Принципы построения триггерных ячеек и их условные обозначения.

Независимо от того, какую функцию выполняют логические элементы И-НЕ либо ИЛИ-НЕ, ячейки могут находиться в двух устойчивых состояниях: 1 и 0. Состоянию 1 соответствует единичный сигнал на выходе Q, состоянию 0 соответствует единичный сигнал на выходе .

--> ЧИТАТЬ ПОЛНОСТЬЮ <--