Курсовая работа: Основы языка VHDL

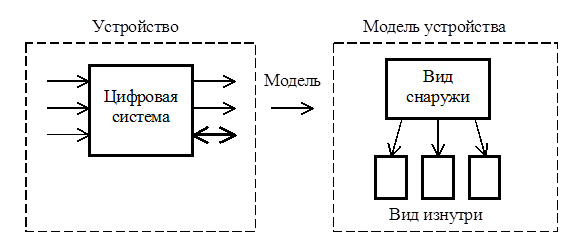

Язык VHDLслужит для описания модели цифрового устройства (прибора, системы). Описание на языке VHDLопределяет внешние связи устройства (“вид снаружи” или интерфейс) и один или несколько “видов изнутри” (см. рис. 1.1). Вид снаружи задает интерфейс устройства, набор сигналов, которыми устройство обменивается с внешним миром. Этот вид описывает абстрактное представление устройства “в целом” и обозначается английским термином entity, что в дословном переводе означает «сущность» и наиболее точно отражает смысл представления. Однако в литературе термин «сущность» не нашел широкого распространения, для обозначения внешнего описания объекта используются термины «интерфейс объекта», «декларативная часть» и другие. В настоящем пособии будет использоваться термин «интерфейс объекта» или просто «интерфейс».

Рис. 1.1. Цифровое устройство и его модель

Вид изнутри определяет функциональные возможности устройства или его структуру. Внутреннее строение объекта определяет архитектура (architecturebody).

Как и в языках программирования, язык VHDLимеет свои правила, в том числе правила описания имен переменных, объектов, типов данных и других параметров. Основные правила языка VHDLописаны в последующих разделах.

1.2 Идентификаторы в языке VHDL

Идентификаторы - это последовательность букв и цифр произвольной длины. Легальными символами являются прописные (A…Z), строчные (a…z), цифры (0…9), знак подчеркивания. Первый символ должен быть буквой, а последний символ не может быть знаком подчеркивания. Строчные и прописные буквы считаются идентичными, например, Count, COUNT и CouNTрассматриваются как один идентификатор. Знаки подчеркивания не должны следовать друг за другом. Комментарии начинаются с двойного дефиса и следуют до конца строки, например,

- это комментарий, он продолжается до конца строки

- это продолжение комментария

entityUARTisend -- это комментарий, который следует за декларацией интерфейса устройства.

Следующие идентификаторы зарезервированы для использования в качестве ключевых слов и не могут быть использованы иначе:

| Abs | Access | after | alias | All |

| And | architecture | array | begin | Block |

| Body | Buffer | case | component | Configu-ration |

| Constant | disconnect | downto | else | Elsif |

| End | Entity | file | for | function |

| generate | Generic | guarded | if | In |

| inout | Is | label | library | linkage |

| loop | Map | mod | nand | New |

| next | Nor | not | null | Of |

| on | Open | or | others | Out |

| package | Port | procedure | process | Range |

| record | Register | rem | select | severity |

| signal | Subtyupe | then | to | Transport |

| type | Units | until | use | vriable |

| wait | When | while | with | Xor |

1.3 Объекты языка VHDL

Объекты это область хранения данных определенного типа. Создаются объекты посредством декларации объекта, например:

variableCOUNT: INTEGER;

В результате порождается объект с именем COUNT, который хранит целочисленную величину. Кроме того, COUNTдекларируется как класс variable.

Объекты – данные могут быть трех классов:

- сonstant(константа) - может хранить отдельное значение определенного типа. Это значение присваивается объекту в начале моделирования и не может изменяться в процессе моделирования.

- variable(переменная) - объект этого класса может хранить отдельное значение определенного типа, однако, в процессе моделирования ему могут присваиваться различные значения. Для этого используются выражения присваивания (variableassignmentstatement).

- signal(сигнал) – объект данного класса имеет предыдущее значение, имеет текущее значение и набор последующих значений.

Объекты класса signalмоделируют проводные соединения в схемах, в то время как переменные (variable) и константы (constant) используются для моделирования поведения схемы, они аналогичны объектам, используемым в языках программирования Cи Pascal.

Декларация констант

Декларации объектов (objectdeclaration) имеют целью дать имя объекту, объявить его тип, класс и даже присвоить значение. Примеры деклараций констант описаны ниже:

constantRISE_TIME: TIME:= 10ns;

constantBUS_WIDTH: INTEGER:= 8:

В первом случае объявляется объект RISE_TIME, который хранит значение типа TIME, объекту в начале моделирования присваивается величина 10 наносекунд. Во втором случае объявляется, что BUS_WIDTH(ширина шины) типа INTEGER(целое) и ей присвоено значение 8.

Декларация переменных

Примеры деклараций объектов класса variableприведены ниже:

variable CTRL_STATUS: BIT_VECTOR(10 downto 0);

variable SUM: INTEGER range 0 to 100 := 10;

variableFOUND, DONE: BOOLEAN;

В первом случае декларируется переменная CTRL_STATUSкак массив из 11 элементов, причем, каждый элемент типа BIT. Во втором случае переменная SUMдекларируется как целое, лежащее в диапазоне от 0 до 100, в начале моделирования переменной присваивается значение 10. Если переменной в начале моделирования не задано значение, то используется значение по умолчанию. Им служит самое “левое” значение в наборе значений данного типа. Например, переменная типа BOOLEANимеет набор значений (FALSE, TRUE) и в третьем примере начальное значение переменных FOUNDи DONEбудет взято по умолчанию, т.е. FALSE.

Декларация сигналов

Декларации объектов класса signalсхожи с декларациями переменных:

signal CLOCK: BIT;

--> ЧИТАТЬ ПОЛНОСТЬЮ <--