Курсовая работа: Основы языка VHDL

endhalf_adder;

Здесь описание с именем half_adderимеет два входных порта, aи b(in– означает входной порт), и два выходных порта, sumи carry(out– означает выходной порт). Тип портов определен как BIT– означает, что сигналы на линиях портов могут принимать значения: ‘0’ или ‘1’.

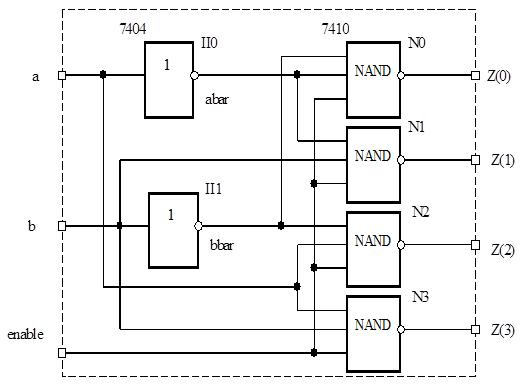

Другим примером может послужить дешифратор, показанный на рис. 1.3.

entity dec2x4 is

port(a, b, enable: in BIT; z: out BIT_VECTOR (0 to 3));

enddec2x4;

Здесь описание с именем dec2x4 имеет три входных порта и четыре выходных. Выходные порты описаны как массив. BIT_VECTOR– это одномерный массив, диапазон задается параметром Z(0 to3).

Рис. 1.3. Декодер 2х4

Каждый интерфейсный порт может функционировать в следующих режимах:

in– значение порта только считывается для использования внутри модели,

out– значение порта может только обновляться моделью, но не считывается,

inout– двунаправленный порт, значение считывается и обновляется моделью,

buffer– буферный порт, значение считывается и обновляется моделью, но источником сигнала может быть либо буфер, либо одиночный источник.

1.9 Архитектура

Архитектура (architecturebody) моделирует взгляд на устройство “изнутри”. Устройство может рассматриваться под разными углами и описываться по-разному. Оно может предстать либо как композиция более простых модулей (структурный стиль моделирования), либо как набор параллельно исполняемых алгоритмов (стиль dataflow), либо описано как процесс последовательного исполнения операций (стиль “поведенческий”), либо может быть раскрыто сочетанием указанных стилей.

С одним интерфейсом типа entity может быть связано несколько архитектур. Рассмотрение архитектурных стилей начнем с поведенческого (behavioralstyle).

Поведенческое описание

Функционирование устройства рассматривается как процесс последовательного вычисления выражений, входящих в process. Толчком к запуску процесса является изменение (event-событие) какого либо сигнала, из входящих в список “воспринимаемых” сигналов (sensitivitylist). Этот список внешне очень похож на список параметров в других языках высокого уровня. Рассмотрим поведенческую модель декодера dec2х4 (рис.1.3). Декларация интерфейса его уже приводилась, а теперь она будет пополнена архитектурой поведенческого типа.

entity dec2x4 is

port(a, b, enable: in BIT; z: out BIT_VECTOR (0 to 3));

end dec2x4;

architecture dec_seq of dec2x4 is

begin

process (a, b, enable)

variable abar, bbar: BIT;

begin

abar:= not a; --выражение 1

bbar:= not b; -- выражение 2

If enable = ‘1’ then -- выражение 3

z(3) <= not (a and b); -- выражение 4