Курсовая работа: Основы языка VHDL

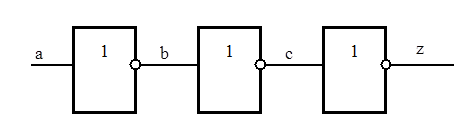

Рис. 1.7. Цепочкаинверторов

entity fast_inverter is

port (a: in BIT; z: out BIT);

end fast_inverter;

architecture delta_delay of fast_inverter is

signal b,c: BIT;

begin

z <= not c; -- выражение1

c<= notb; --выражение 2

b<= nota; --выражение 3

enddelta_delay;

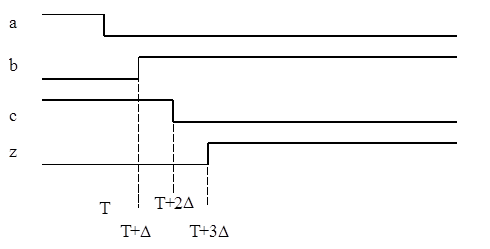

В выражениях 1, 2 и 3, присваивающих значения переменным z, c, b, подразумевается задержка D. Например, в момент Tпроисходит изменение сигнала a. Запускается процесс вычисления выражения 3 и через задержку D переменной bбудет присвоено новое значение (в момент T+D). В свою очередь изменение сигнала bзапустит процесс вычисления выражения 2 и значение сигнала с будет обновлено в момент T+2D. Изменение сигнала с приведет к запуску процесса вычисления выражения 1 и значение сигнала zбудет изменено в момент T+3D. Временные соотношения в схеме иллюстрирует рис. 1.8.

Рис. 1.8. Временные соотношения в цепочке инверторов.

Структурное описание.

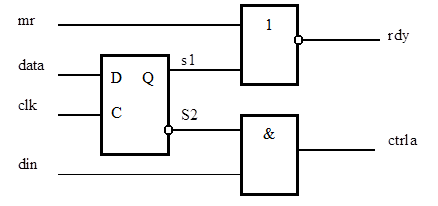

Структурное описание интерпретирует устройство как набор компонентов, связанных между собой сигналами. Грубо говоря - это таблица соединений (netlist). Рассмотрим простую схему управления (рис.1.8) и ее структурную модель.

Рис. 1.9. Устройство местного управления

entityctr_lckis

port (data, mr, clk, din: in BIT; rdy, ctrla:out Bit);

end ctr_lck;

architecture str_view of ctr_lck is

component AND2 -- декларируетсякомпонентAND2

port (x,y in BIT; z: out BIT);

end component;

component DFF -- декларируется компонент DFF

port (d, clock: in BIT; Q,NOTQ: out BIT);

end component;

component NOR2 -- декларируется компонент NOR2