Курсовая работа: Основы языка VHDL

whileбулевскоe_выражение

Пример использования схемы:

J:=0;SUM:=10;

WH-LOOP: while J<20 loop -- loop имеет ярлык WH_LOOP

SUM := SUM * 2;

J:=J+3;

end loop;

Выражения в теле loopвыполняются одно за другим и эта последовательность повторяется, пока условие J<20 истинно.

Третьей cхемой является конструкция, в которой итерационная схема не задается и выход из loopосуществляется с использованием выражений: exit, nextили return, например:

SUM:=1;J:=0;

L2: loop--loopимеет ярлык

J:=J+21;

SUM := SUM* 10;

exit when SUM > 100;

endloopL2;

В этом примере выражение exitзаставляет выходить из петли L2 когда SUMстановится больше 100. При отсутствии выражения exitloopбудет исполняться бесконечно.

1.7 Параллельные операторы

К параллельным операторам (Concurrent Statements) оператор process, оператор параллельного вызова процедуры, оператор конкретизаци компонента, оператор генерации (generate) и другие. Параллельные операторы определяют параллельное поведение схем, порядок их выполнения не зависит от их появления внутри блока.

Рассмотрим кратко оператор process. В общем виде он может быть записан следующим образом.

[имя процесса:][postponed] process [(список)]

раздел деклараций

begin

операторы

endprocess[имя процесса];

Имя процесса и ключевое слово [postponed] являются необязательными и часто отсутствуют. Список, находящийся после ключевого слова process, хотя и является необязательным, на практике используется достаточно часто для указания сигналов запуска. Перед ключевым словом могут находиться различного рода декларации типов, констант атрибутов и т. д.

Хотя процесс является параллельным оператором, он может содержать последовательные операторы. Внутри процессов не мегут быть декларированы сигналы.

1.8 Описание интерфейса устройства

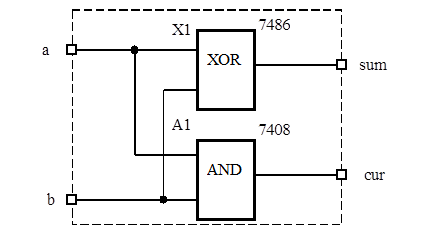

В начале главы уже говорилось, что на моделируемое устройство в первую очередь следует посмотреть со стороны (“вид снаружи”) и для этого “черного ящика” определить интерфейс с внешним миром. Такая задача решается в VHDL декларацией интерфейса entity. Она задает имя описания, имена интерфейсных портов, направление передачи, тип портов. Порт – это сигнальная линия (шина), с помощью которой устройство (модель) взаимодействуют с окружающей средой. Например, для полусумматора (рис. 1.2) декларация будет выглядеть следующим образом:

Рис. 1.2. Полусумматор

entity half_adder is