Курсовая работа: Основы языка VHDL

z(1) <= not (abar and b); -- выражение 6

z(0) <= not (abar and bbar); -- выражение 7

else z <= “1111”;

end if;

end process;

enddec_seq;

Архитектура имеет свое имя dec_seq. О принадлежности архитектуры к описанию интерфейса dec2х4 говорит выражение: dec_seqofdec2x4. Список сигналов, которыми запускается процесс, дан в скобках: process(a, b, enable). До начала процесса, если необходимо, декларируются переменные variableabar, bbar: BIT. Зона действия их ограничена данным процессом (от beginдо endprocess). Предположим, что в момент Tпроизошло изменение сигнала а. Новое значение переменной abar(выражение 1) вычисляется и присваивается без задержки – мгновенно (в качестве знака присваивания в данном случае используется =). Без задержки будут вычислены выражения 2 и 3.

Далее в ходе процесса одно за другим вычисляются выражения от 4 до 7, а новые значения сигналам z(0), z(1), z(2), z(3) будут присвоены (в качестве символа оператора присвоения используется <= ) лишь через некоторую, пусть даже фиктивную (бесконечно малую), задержку D. Это существенное отличие процедур присвоения для переменных и для сигналов.

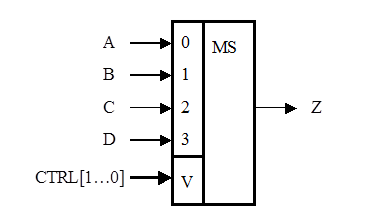

Рассмотрим пример мультиплексора 4х1 (рис.1.4). Четыре входных сигнала A, B, Cи Dвыводятся через один порт Z. Коммутация осуществляется сигналом CTRL.

Рис. 1.4. Мультиплексор4х1.

entity MUX is

port (A, B, C, D: in BIT; CTRL: in BIT_VECTOR(0 to 1);

Z: out BIT);

end MUX;

architecture MUX_BEHAVIOR of MUX is

begin

PMUX: process (A, B, C, D, CTRL)

variable TEMP: BIT;

begin

case CTRL is

when "00" => TEMP := A:

when "01" => TEMP := B;

when "10" => TEMP := C;

when "11" => TEMP := D;

end case;

Z <= TEMP;

end process PMUX;

end MUX_BEHAVIOR;