Курсовая работа: Основы языка VHDL

package maxplus2 is

component a_7486

port (a_2: in BIT;

a_3: in BIT;

a_1: out BIT);

end component;

component a_7408

port (a_2: in BIT;

a_3: in BIT;

a_1: out BIT);

endmaxplus2;

Файл maxplus2 при компиляции может быть помещен в библиотеку, например, с названием altera. Ссылка на библиотеку позволит не декларировать компоненты в архитектуре:

libraryaltera;

use altera.maxplus2.all;

entity half_adder is

port(a, b: in BIT; sum, cur: out BIT);

end half_adder;

architecture h_a_str of half_adder is

begin

X1: a_7486 port map (a, b, sum);

A1: a_7408 port map (a, b, cur);

endh_a_str;

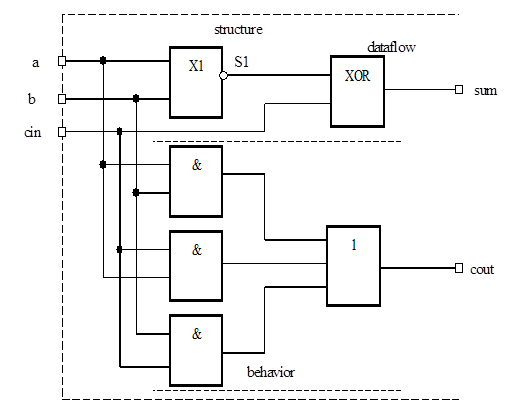

Комбинированное описание архитектуры

В едином теле архитектуры можно комбинировать все рассмотренные выше стили моделирования. В качестве примера рассмотрим одноразрядный полный сумматор (рис.1.5).

Сумматор представлен выражением 1, создающим экземпляр X1 компонента а_7486 (из библиотеки altera.maxplus2), и задающим отображение портов и сигнала сущности (сумматора) на порты компонента. Это структурный стиль.

Выражение 2 - это process, поведенческий стиль, и выражение 3 – это стиль dataflow.

Рис.1.10. Одноразрядный сумматор

libraryaltera;

use altera.maxplus2.all;