Курсовая работа: Основы языка VHDL

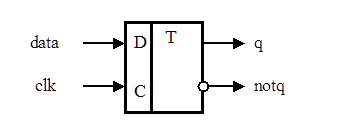

Для описания синхросигналов обычно используется атрибу EVENT. Он истинен когда происходит “событие” - изменение сигнала. Например, поведение D-триггера, показанного на рис.1.5, можно описать так:

Рис.1.5. D-триггер

entity dff is

port (data, clk: in BIT

q, notq: out BIT);

end dff;

architecture behav of dff is

begin

process (clk)

begin

if (clk’event and clk = ‘1’) then

q <= data;

notq <= not data;

end if;

end process;

end behav;

Выражение (clk’eventandclk= ‘1’) задает условие: если сигнал clk меняется с ‘0’ на ‘1’

Потоковое описание (dataflow)

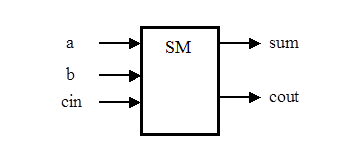

Dataflow- означает поток данных. Описание в стиле dataflowиспользует в архитектуре параллельно вычисляемые выражения. Количество параллельно вычисляемых выражений может быть любым. Так как вычисления происходят параллельно, то порядок записи выражений не имеет значения. Толчком к началу вычислений является изменение любого из сигналов, входящих в выражения. Рассмотрим модель одноразрядного сумматора, показанного на рис.1.6.

Рис.1.6. Одноразрядныйсумматор

entity full_adder is

port (a, b, cin: in BIT; sum, cout: out BIT);

end full_adder;

architecture full_ad_conc of full_adder is

begin

sum <= (a xor b) xor cin after 15 ns;

cout <= (a and b)or(b and cin)or(cin and a) after 10ns;

endfull_ad_conc;