Курсовая работа: Расчет параметров структуры интегрального n-p-n транзистора и определение технологических режимов его изготовления

1 стадия: Т1 = 1100 0 С и t1 = 5125,96 с; 2 стадия: Т2 = 1100 0 С и t2 = 11261,85 с.

Диффузия фосфора

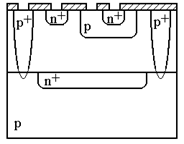

Рис. 9.13.

21) Фотолитография под контактные окна.

Фотолитография под контактные окна

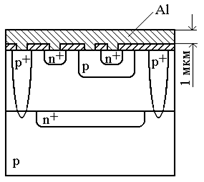

Рис. 9.14.

22) Контроль электрических параметров элементов. Измерения проводятся при помощи зарядовой установки и ПИХЛ22.

23) Химическая обработка.

24) Напыление алюминия.

Напыление алюминия

Рис. 9.15.

25) Фотолитография по алюминию.

Структура эпитаксиального n-p-n-транзистора

Рис. 9.16.

26) Вплавление алюминия.

ТВПЛ < ТЭВТ Al-Si = 570 0 С.

ТВПЛ = 565 0 С, t = 3 мин

Заключение

В данном курсовом проекте при заданном напряжении коллектор-база VКБ = 15 В, ширине активной базы Wа = 0,7 мкм рассчитаны параметры структуры транзистора и определены технологические режимы ее изготовления.

Скрытый слой глубиной xjСС =8,49 мкм формируется по стандартным режимам имплантации (Е=50 кэВ, Ф=500 мкКл/см2 ) и последующей термической диффузии ионов сурьмы (ТСС =1220 0 С, tCC =12 ч). Эпитаксиальный слой толщиной hЭС![]() 6 мкм и удельным сопротивлением ЭС =0,4 Ом* см наращивается на кремниевую пластину ЭКДБ-10. Параметры эпитаксии: температура ТЭ =1150 0 С, скорость наращивания vЭН = 0,2 мкм/мин, длительность эпитаксиального наращивания tЭ =38 мин.

6 мкм и удельным сопротивлением ЭС =0,4 Ом* см наращивается на кремниевую пластину ЭКДБ-10. Параметры эпитаксии: температура ТЭ =1150 0 С, скорость наращивания vЭН = 0,2 мкм/мин, длительность эпитаксиального наращивания tЭ =38 мин.

Разделительные дорожки формируются путем диффузии бора с поверхности ЭС вглубь до смыкания с подложкой (глубина залегания xjРD = 7,062 мкм). Разделительная диффузия проводится в два этапа: Т1 =1150 0 С и t1 =9,08 мин, Т2 =1220 0 С и t2 =1,43 ч. Формирование базовой области проводим методом имплантации ионов бора (Е=50 кэВ, Ф=809 мкКл/см2 ) с последующей термической диффузией имплантированных ионов (Т=1150 0 С и t=77,55 мин). Эмиттерные области формируются путем последовательной диффузии фосфора Р (Т1 =1100 0 С и t1 =5125,96 с, Т2 =1100 0 С и t2 =11261,85 с). Величина размывания скрытого слоя в эпитаксиальный слой в процессе термообработки КЭСС равна cc = 0,36 мкм.

Областью применения результатов данного проектирования может являться расчет кремниевых эпитаксиально-планарных транзисторов.

Список использованных источников

1. Курносов А.И., Юдин В.В. Технология производства полупроводниковых приборов и интегральных микросхем. Учеб. пособие для вузов по спец. «Полупроводники и диэлектрики» и «Полупроводниковые приборы». – 3-е изд., перераб. и доп. – М.: Высш. шк., 1986. – 386 с., ил.

Приложение 1