Курсовая работа: Устройство разделения цифрового потока данных

Содержание

Часть 1. Описание устройства и принципов его работы

1.1 Обоснование выбора темы

1.2 Краткое описание и возможные варианты исполнения

1.2.1 Подключение микросхемы ЦАП AD1851

1.2.1.1 Способ 1. Прерывание тактового сигнала

1.2.1.2 Способ 2. Использование регистра сдвига

1.2.1.3 Способ 3. Регистр сдвига для подключения по шине I2S

1.2.2 Подключение микросхемы ЦАП AD1852 (AD1853)

Часть 2. Схемная реализация

2.1 Определение требований к применяемым цифровым микросхемам

2.2 Схемы электрические принципиальные

2.2.1 Схема устройства разделения потока данных для подключения микросхемы ЦАП AD1851

2.2.2 Схема устройства разделения потока данных для монофонического подключения микросхемы ЦАП AD1852 (AD1853)

2.2.3 Общие замечания к схемам

Часть 3. Временные диаграммы

3.1 Временная диаграмма работы устройства разделения данных для микросхемы ЦАП AD1851

3.2 Временная диаграмма работы устройства разделения данных для микросхемы ЦАП AD1852

Часть 4. Реализация схемы в проекте VHDL

Выводы

Часть 1. Описание устройства и принципов его работы

1.1 Обоснование выбора темы

В последнее время техника и технология стремительно развиваются. Эта область также не обходит и электронику. Каждый день выходят новые микросхемы и пополняется элементная база. Однако также в промышленности прослеживается тенденция упрощения и удешевления производства, что приводит к массовому выпуску дешевой, красочной и далеко не самого высокого качества (если не сказать весьма низкого) аппаратуры. Эти тенденции также затрагивают и область аудиотехники.

К сожалению, человеку, желающему качественно слушать любимые записи, сейчас приходится либо смириться с вышесказанным, либо платить достаточно большие суммы за качественную аппаратуру. Есть правда и еще один вариант: эту аппаратуру можно собрать своими руками на современной элементной базе.

Одной из наиболее значимых частей аудио тракта (с учетом распространения цифрового аудио) бесспорно является ЦАП. От качества этого модуля напрямую будет зависеть качество получаемого звукового сигнала. При этом для достижения желаемых результатов часто приходится использовать микросхемы с отличающимися протоколами обмена информацией. Таким образом, встает вопрос о преобразовании цифровых форматов данных.

Наиболее часто встречается ситуация, когда приемник цифрового сигнала способен выдавать данные в формате IIS (наиболее универсальный и полнофункциональный формат), а микросхема ЦАП способна принимать данные в формате Right Justifited. Также следует учесть то, что приемник сигнала выдает данные обоих стерео каналов по одной шине в то время как наиболее качественные микросхемы ЦАП являются монофоническими. Именно вопросу преобразования цифрового потока из формата IIS в Right Justifited с одновременным разделением на каналы и посвящена половина данной курсовой работы. Вторая половина посвящена разделению каналов в случае использования монофонического включения стерео-ЦАП.

1.2 Краткое описание и возможные варианты исполнения

В рамках данной курсовой работы предполагается использовать микросхемы ЦАП AD1851 (16bitmono) и AD1852 (24bit 192kHzstereo) производства AnalogDevices.

1.2.1 Подключение микросхемы ЦАП AD1851

Рассмотрим цифровой интерфейс AD1851:

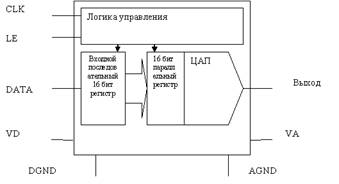

Схематически внутреннее устройство микросхемы можно представить следующим образом:

Рис. 1. – Внутренняя структура AD1851

Согласно документации микросхема имеет три цифровых входа: CLK, DATA и LE. Данные поступают во входной последовательный регистр сдвига через вход DATA и тактируются по переднему фронту сигнала CLK. Емкость входного регистра составляет 16 бит. Когда во входной регистр полностью загружены данные, по заднему фронту сигнала LE информация переносится в параллельный 16 битный регистр непосредственно модуля ЦАП, при этом выходная величина (микросхема способна работать как в варианте с токовым выходом, так и в варианте с выходом по напряжению) обновляется и удерживается до следующего перепада сигнала LE от высокого уровня к низкому. Временная диаграмма необходимых входных сигналов представлена на рисунке 2:

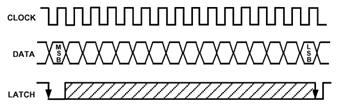

Рис. 2. – Временная диаграмма входных сигналов AD1851

Данный формат сигналов способны выдавать практически все цифровые фильтры. В большинстве случаев они уже имеют входы предустановки под микросхемы ЦАП различной разрядности и отдельные выводы данных (DOR, DOL) для микросхем правого и левого каналов.

Тем не менее, при желании построить ЦАП без передискретизации (достаточно нашумевшее направление в области современного высококачественного аудио) от их применения приходится отказаться. При этом микросхемы ЦАП подключаются через согласующую логику к микросхеме приемника цифровых данных.

Наиболее простым для работы выходным форматом данных цифровых приемников является формат Right Justifited:

Рис. 3. – формат передачи данных Right Justifited

В этом формате данные левого и правого каналов передаются последовательно по одному проводнику SDATA, данные какого именно канала передаются в данный момент, определяет состояние сигнала LRCLK, тактовые импульсы передаются посредством сигнала SCLK. Первыми передаются данные левого канала (LRCLK=’1’), затем правого (LRCLK=’0’). Данные поступают в формате MSBFirst, и выровнены относительно перепада сигнала LRCLK по правому (заднему) фронту.

Для правильного преобразования данных необходимо загрузить данные каждого канала в свою микросхему ЦАП и одновременно подать сигнал обновления LE. В противном случае мы получим сдвиг по фазе между аналоговыми сигналами правого и левого каналов, зависящий от частоты сигнала.

Классический случай описан Паулем Шкритеком в "Справочном руководстве по звуковой схемотехнике", издательство "Мир", глава 17.7.1 "Преобразователи Ц/А в мультиплексном режиме". Цитата: "Если данные на ЦАП двух каналов поступают со сдвигом во времени на dT, то между каналами возникает сдвиг по фазе, зависящей от частоты: dF=360*f*dT". И далее: "В случае, когда оба канала обслуживает один ЦАП, работающий с временным уплотнением, временной сдвиг в нормальных условиях составляет dT=T/2=11.3 мксек, что вызывает фазовый сдвиг между сигналами левого и правого канала dF=82 градуса на частоте 20кГц".

Существует несколько способов сделать необходимое соединение.

1.2.1.1 Способ 1. Прерывание тактового сигнала

Как уже известно, данные в микросхеме ЦАП сначала попадают во входной последовательный регистр, тактируемые сигналом CLK. В формате Right Justifited данные передаются выровненными по правому фронту сигнала LRCLK, данные левого канала первыми, данные правого канала последующими. Выход микросхем ЦАП необходимо обновить по загрузке данных обоих каналов, т.е. по нарастающему фронту сигнала LRCLK. При отсутствии сигнала CLK данные во входной регистр ЦАП грузиться не будут. При загрузке в регистр свыше 16 бит данных, во входном регистре остаются лишь последние 16 бит информации. Таким образом, необходимо загрузить данные левого канала в одну микросхему ЦАП, затем прервать поступление тактовых импульсов на нее и дождаться загрузки данных правого канала во вторую микросхему. Сигналом обновления при этом будет инвертированный сигнал LRCLK. Он же будет управляющим для прерывателя тактовых импульсов. Входы данных обоих микросхем ЦАП при таком включении параллелятся.

Данную операцию можно произвести с помощью всего одной логической микросхемы:

Рис. 4. – формирование сигналов методом прерывания тактовых импульсов

К сожалению, данный метод не является идеальным, поскольку некоторые микросхемы ЦАП отказываются работать в таком включении. Например, Алекс Петровский на своем сайте писал, что в таком включении отказались работать микросхемы PCM1704 производства Burr-Brown и AD1856 производства AnalogDevices.Это происходит в основном из-за требования непрерывности тактового сигнала или из-за повышенной чувствительности логических цепей микросхемы к временным соотношениям между сигналами.

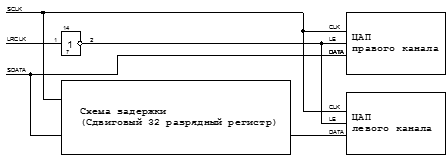

1.2.1.2 Способ 2. Использование регистра сдвига

Для использования этого метода также удобно воспользоваться выходным форматом Right Justifited приемника цифровых сигналов. При этом необходимо отметить, что стандартной длиной последовательности данных за один отсчет является 64 бита. При этом на каждый канал приходится по 32 тактовых импульса. Первые 16 импульсов при этом не используются, по оставшимся 16 передаются данные. При этом первый бит данных правого канала передается через 32 тактовых импульса после первого бита данных левого канала. Таким образом, если задержать всю последовательность данных на 32 тактовых импульса, то на выходе схемы задержки будут данные левого канала в тот момент, когда в исходном сигнале будут передаваться данные правого канала. В качестве такой схемы очень удобно использовать 32 разрядный сдвиговый регистр. Обновление выхода микросхем ЦАП происходит по нарастающему фронту сигнала LRCLK. Схематически это можно изобразить следующим образом:

--> ЧИТАТЬ ПОЛНОСТЬЮ <--